# **SPIM Instructions**

Instructions marked with a dagger (†) are pseudoinstructions.

# **Arithmetic Instructions**

In all instructions below, Src2 can either be a register or an immediate value (a 16 bit integer). The immediate forms of the instructions are only included for reference. The assembler will translate the more general form of an instruction (e.g., add) into the immediate form (e.g., addi) if the second argument is a constant.

### Absolute Value

Put the absolute value of the integer from register Rsrc in register Rdest:

abs Rdest, Rsrc

Absolute Value <sup>†</sup>

### Add

Put the sum of the integers from registers Rs and Rt (or Imm) into register Rd:

| add                                             | add Rd, Rs, Rt Addition (with overflow) |    |                                    |                   |                   |      |

|-------------------------------------------------|-----------------------------------------|----|------------------------------------|-------------------|-------------------|------|

| Γ                                               | 0                                       | Rs | $\operatorname{Rt}$                | Rd                | 0                 | 0x20 |

| L                                               | 6                                       | 5  | 5                                  | 5                 | 5                 | 6    |

| add                                             | u Rd, Rs, R                             |    |                                    | Addition (v       | without overflow) |      |

|                                                 | 0                                       | Rs | $\operatorname{Rt}$                | Rd                | 0                 | 0x21 |

| L                                               | 6                                       | 5  | 5                                  | 5                 | 5                 | 6    |

| add                                             | i Rt, Rs, I                             |    | Addition Immediate (with overflow) |                   |                   |      |

|                                                 | 8                                       | Rs | $\operatorname{Rt}$                |                   | Imm               |      |

| L                                               | 6                                       | 5  | 5                                  |                   | 16                |      |

| addiu Rt, Rs, Imm Addition Immediate (without o |                                         |    |                                    | without overflow) |                   |      |

|                                                 | 9                                       | Rs | $\operatorname{Rt}$                |                   | Imm               |      |

| L                                               | 6                                       | 5  | 5                                  |                   | 16                |      |

|                                                 |                                         |    |                                    |                   |                   |      |

### Subtract

Put the difference of the integers from register Rs and Rt into register Rd:

| sub Rd, Rs, Rt Subtract (with over)         |              |    |    |    | t (with overflow) |                        |

|---------------------------------------------|--------------|----|----|----|-------------------|------------------------|

|                                             | 0            | Rs | Rt | Rd | 0                 | 0x22                   |

|                                             | 6            | 5  | 5  | 5  | 5                 | 6                      |

| subu Rd, Rs, Rt Subtract (without overflow) |              |    |    |    |                   |                        |

| sul                                         | ou Rd, Rs, F | lt |    |    | Subtract (v       | without overflow)      |

| sul                                         | ou Rd, Rs, F | Rs | Rt | Rd | Subtract (i       | without overflow) 0x23 |

# Multiply

Put the product of registers  $\tt Rsrc1$  and  $\tt Src2$  into register <code>Rdest:</code>

| mul Rdest, Rsrc1, Src2   | Multiply (without overflow) $^{\dagger}$       |

|--------------------------|------------------------------------------------|

| mulo Rdest, Rsrc1, Src2  | Multiply (with overflow) $^{\dagger}$          |

| mulou Rdest, Rsrc1, Src2 | Unsigned Multiply (with overflow) $^{\dagger}$ |

Multiply the contents of registers Rs and Rt. Leave the low-order word of the product in register lo and the high-word in register hi:

| mul | t Rs, Rt  |    |    |    | Multiply               |

|-----|-----------|----|----|----|------------------------|

|     | 0         | Rs | Rt | 0  | 0x18                   |

|     | 6         | 5  | 5  | 10 | 6                      |

|     |           |    |    |    |                        |

| mul | tu Rs, Rt |    |    |    | Unsigned Multiply      |

| mul | tu Rs, Rt | Rs | Rt | 0  | Unsigned Multiply 0x19 |

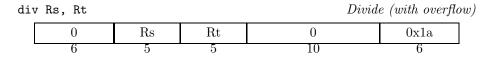

### Divide

Divide the integer in register Rs by the integer in register Rt. Leave the quotient in register lo and the remainder in register hi:

| div | vu Rs, Rt |    |                     | Divide (v | without overflo | ow) |

|-----|-----------|----|---------------------|-----------|-----------------|-----|

|     | 0         | Rs | $\operatorname{Rt}$ | 0         | 0x1b            |     |

|     | 6         | 5  | 5                   | 10        | 6               | •   |

Note that if an operand is negative, the remainder is unspecified by the MIPS architecture and depends on the conventions of the machine on which SPIM is run.

Put the quotient of the integers from register Rsrc1 and Src2 into register Rdest:

div Rdest, Rsrc1, Src2 divu Rdest, Rsrc1, Src2 Divide (with overflow) <sup>†</sup> Divide (without overflow) <sup>†</sup>

#### Negative

Put the negative of the integer from register Rsrc into register Rdest:

neg Rdest, Rsrc negu Rdest, Rsrc Negate Value (with overflow) <sup>†</sup> Negate Value (without overflow) <sup>†</sup>

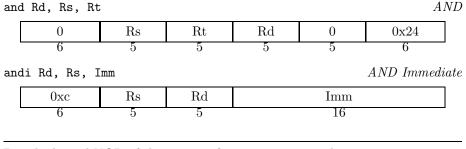

### **Logical Operations**

Put the logical AND of the integers from register Rs and register Rt (or the zero-extended immediate value Imm) into register Rd:

Put the logical NOR of the integers from register Rs and Rt into register Rd:

| noi | r Rd, Rs, Rt |    |    |    |   | N    | OR |

|-----|--------------|----|----|----|---|------|----|

|     | 0            | Rs | Rt | Rd | 0 | 0x27 |    |

|     | 6            | 5  | 5  | 5  | 5 | 6    |    |

Put the bitwise logical negation of the integer from register Rsrc into register Rdest:

not Rdest, Rsrc

$NOT^{\dagger}$

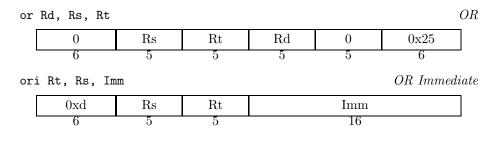

Put the logical OR of the integers from register  $\mathtt{Rs}$  and  $\mathtt{Rt}$  (or  $\mathtt{Imm})$  into register <code>Rd</code>:

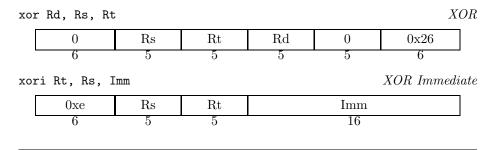

Put the logical XOR of the integers from register  $\tt Rsrc1$  and  $\tt Src2$  (or  $\tt Imm)$  into register <code>Rdest:</code>

### Remainder

Put the remainder from dividing the integer in register Rsrc1 by the integer in Src2 into register Rdest:

| rem Rdest, Rsrc1, Src2  | Remainder †                     |

|-------------------------|---------------------------------|

| remu Rdest, Rsrc1, Src2 | Unsigned Remainder $^{\dagger}$ |

Note that if an operand is negative, the remainder is unspecified by the MIPS architecture and depends on the conventions of the machine on which SPIM is run.

# **Rotate and Shift Instructions**

Rotate the contents of register Rsrc1 left (right) by the distance indicated by Src2 and put the result in register Rdest:

| rol | Rdest, | Rsrc1, | Src2 | Rotate Left $^{\dagger}$  |

|-----|--------|--------|------|---------------------------|

| ror | Rdest, | Rsrc1, | Src2 | Rotate Right $^{\dagger}$ |

Shift the contents of register Rt left (right) by the distance indicated by Sa (Rs) and put the result in register Rd:

| sll Rd, Rt, Sa                                       | L                  |              |                       | S                       | Shift Left Logical                                        |

|------------------------------------------------------|--------------------|--------------|-----------------------|-------------------------|-----------------------------------------------------------|

| 0                                                    | Rs                 | Rt           | Rd                    | Sa                      | 0                                                         |

| 6                                                    | 5                  | 5            | 5                     | 5                       | 6                                                         |

| sllv Rd, Rt, Rs Shift Left Logical Variabl           |                    |              |                       |                         |                                                           |

| 0                                                    | Rs                 | Rt           | Rd                    | 0                       | 4                                                         |

| 6                                                    | 5                  | 5            | 5                     | 5                       | 6                                                         |

| sra Rd, Rt, Sa                                       | L                  |              |                       | Shift 1                 | Right Arithmetic                                          |

| 0                                                    | Rs                 | Rt           | Rd                    | Sa                      | 3                                                         |

| 6                                                    | 5                  | 5            | 5                     | 5                       | 6                                                         |

| srav Rd, Rt, Rs Shift Right Arithmetic Variable      |                    |              |                       |                         |                                                           |

| srav Rd, Rt, R                                       | ls                 |              | Sh                    | ift Right Ari           | thmetic Variable                                          |

| srav Rd, Rt, R                                       | ls<br>Rs           | Rt           | Sh <sup>i</sup><br>Rd | ift Right Aria          | thmetic Variable                                          |

|                                                      | _                  | Rt<br>5      |                       | г - т                   |                                                           |

| 0                                                    | Rs<br>5            |              | Rd                    | 0 5                     | 7                                                         |

| 0 6                                                  | Rs<br>5            |              | Rd                    | 0 5                     | 7<br>6                                                    |

| 0<br>6<br>srl Rd, Rt, Sa                             | Rs<br>5            | 5            | Rd<br>5               | 0<br>5<br><i>Sh</i>     | 7<br>6<br>ift Right Logical                               |

| 0<br>6<br>srl Rd, Rt, Sa<br>0                        | Rs<br>5<br>Rs<br>5 | 5<br>Rt      | Rd<br>5<br>Rd         | 0<br>5<br>Sh<br>Sa<br>5 | 7<br>6<br>ift Right Logical<br>2                          |

| 0<br>6<br>srl Rd, Rt, Sa<br>0<br>6                   | Rs<br>5<br>Rs<br>5 | 5<br>Rt      | Rd<br>5<br>Rd         | 0<br>5<br>Sh<br>Sa<br>5 | 7<br>6<br>ift Right Logical<br>2<br>6                     |

| 0<br>6<br>srl Rd, Rt, Sa<br>0<br>6<br>srlv Rd, Rt, R | Rs<br>5<br>Rs<br>5 | 5<br>Rt<br>5 | Rd<br>5<br>Rd<br>5    | 0<br>5<br>Shift Right   | 7<br>6<br>ift Right Logical<br>2<br>6<br>Logical Variable |

### **Constant-Manipulating Instructions**

Move the immediate imm into register Rdest:

li Rdest, imm

Load Immediate <sup>†</sup>

Load the lower halfword of the immediate imm into the upper halfword of register Rdest. The lower bits of the register are set to 0:

| lu | i Rt, imm       |    |    | Load Upper Immediate |

|----|-----------------|----|----|----------------------|

|    | $0 \mathrm{xf}$ | Rs | Rt | Imm                  |

|    | 6               | 5  | 5  | 16                   |

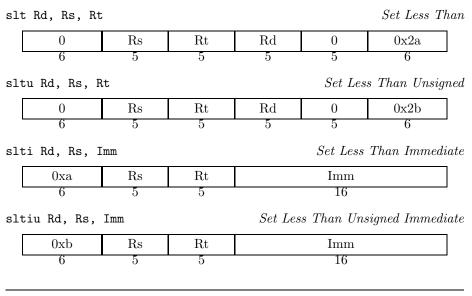

### **Comparison Instructions**

In all instructions below, Src2 can either be a register or an immediate value (a 16 bit integer).

Set register Rdest to 1 if register Rsrc1 equals Src2 and to be 0 otherwise:

seq Rdest, Rsrc1, Src2

Set Equal<sup>†</sup>

Set register Rdest to 1 if register Rsrc1 is greater than or equal to Src2 and to 0 otherwise:

sge Rdest, Rsrc1, Src2 sgeu Rdest, Rsrc1, Src2 Set Greater Than Equal<sup>†</sup> Set Greater Than Equal Unsigned<sup>†</sup>

Set register Rdest to 1 if register Rsrc1 is greater than Src2 and to 0 otherwise:

sgt Rdest, Rsrc1, Src2 sgtu Rdest, Rsrc1, Src2 Set Greater Than <sup>†</sup> Set Greater Than Unsigned <sup>†</sup>

Set register Rdest to 1 if register Rsrc1 is less than or equal to Src2 and to 0 otherwise:

sle Rdest, Rsrc1, Src2 sleu Rdest, Rsrc1, Src2 Set Less Than Equal<sup>†</sup> Set Less Than Equal Unsigned<sup>†</sup> Set register Rdest to 1 if register Rsrc1 is less than Src2 (or Imm) and to 0 otherwise:

Set register Rdest to 1 if register Rsrc1 is not equal to Src2 and to 0 otherwise:

sne Rdest, Rsrc1, Src2

Set Not Equal  $^{\dagger}$

# **Branch and Jump Instructions**

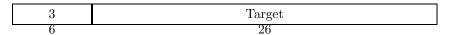

In all instructions below, Src2 can either be a register or an immediate value (integer). Branch instructions use a signed 16-bit offset field; hence they can jump  $2^{15} - 1$  instructions (not bytes) forward or  $2^{15}$  instructions backwards. The jump instruction contains a 26 bit address field.

For branch instructions, the offset of the instruction at a label is computed by the assembler.

Unconditionally branch to the instruction at the label:

b label

Branch pseudoinstruction <sup>†</sup>

Conditionally branch to the instruction at the label if coprocessor z's condition flag is true (false):

| bc <i>z</i> t                                                                                                             | t label                                                                                                                         |     |    | Branch Coprocessor z True                |  |  |

|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|----|------------------------------------------|--|--|

| Γ                                                                                                                         | 0 x 1 z                                                                                                                         | 8   | 1  | Offset                                   |  |  |

| L                                                                                                                         | 6                                                                                                                               | 5   | 5  | 16                                       |  |  |

| bc <i>z</i> i                                                                                                             | f label                                                                                                                         |     |    | Branch Coprocessor z False               |  |  |

| Γ                                                                                                                         | 0 x 1 z                                                                                                                         | 8   | 0  | Offset                                   |  |  |

| L                                                                                                                         | 6                                                                                                                               | 5   | 5  | 16                                       |  |  |

|                                                                                                                           | ditionally br<br>equals the co                                                                                                  |     |    | at the label if the contents of register |  |  |

| beq                                                                                                                       | Rs, Rt, la                                                                                                                      | bel |    | Branch on Equal                          |  |  |

| Γ                                                                                                                         | 4                                                                                                                               | Rs  | Rt | Offset                                   |  |  |

| L                                                                                                                         | 6                                                                                                                               | 5   | 5  | 16                                       |  |  |

| equa                                                                                                                      | Conditionally branch to the instruction at the label if the contents of Rsrc<br>equals 0:beqz Rsrc, labelBranch on Equal Zero † |     |    |                                          |  |  |

| Conditionally branch to the instruction at the label if the contents of register Rsrc1 are greater than or equal to Src2: |                                                                                                                                 |     |    |                                          |  |  |

| bge                                                                                                                       | bge Rsrc1, Src2, labelBranch on Greater Than Equal †bgeu Rsrc1, Src2, labelBranch on GTE Unsigned †                             |     |    |                                          |  |  |

|                                                                                                                           | Conditionally branch to the instruction at the label if the contents of $\mathtt{Rs}$ are greater than or equal to 0:           |     |    |                                          |  |  |

| bgez | Rs, | label |  |

|------|-----|-------|--|

| 0    |     |       |  |

Branch on Greater Than Equal Zero

| 1 | KS I | Offs | set |

|---|------|------|-----|

| 6 | 5 5  | 16   | j   |

Conditionally branch to the instruction at the label if the contents of Rs are greater than or equal to 0. Save the address of the next instruction in register 31:

| bg | ezal Rs, lab | pel | Branch | on Greater Than Equal Zero And Lin | nk |

|----|--------------|-----|--------|------------------------------------|----|

|    | 1            | Rs  | 0x11   | Offset                             |    |

|    | 6            | 5   | 5      | 16                                 |    |

Conditionally branch to the instruction at the label if the contents of register Rsrc1 are greater than Src2:

bgt Rsrc1, Src2, label bgtu Rsrc1, Src2, label Branch on Greater Than <sup>†</sup> Branch on Greater Than Unsigned <sup>†</sup>

Conditionally branch to the instruction at the label if the contents of Rs are greater than 0:

#### bgtz Rs, label

Branch on Greater Than Zero

| 7 | Rs | 0 | Offset |

|---|----|---|--------|

| 6 | 5  | 5 | 16     |

Conditionally branch to the instruction at the label if the contents of register Rsrc1 are less than or equal to Src2:

| ble  | Rsrc1,   | Src2, | label |

|------|----------|-------|-------|

| bleu | . Rsrc1, | Src2, | label |

Branch on Less Than Equal<sup>†</sup> Branch on LTE Unsigned<sup>†</sup>

Conditionally branch to the instruction at the label if the contents of Rs are less than or equal to 0:

| ble | ez Rs, label | -  |   | Branch on Less Than Equal Zero |

|-----|--------------|----|---|--------------------------------|

|     | 6            | Rs | 0 | Offset                         |

|     | 6            | 5  | 5 | 16                             |

Conditionally branch to the instruction at the label if the contents of Rs are less than 0. Save the address of the next instruction in register 31: bltzal Rs, label Branch on Less Than And Link

| 1 | Rs | 0x10 | Offset |

|---|----|------|--------|

| 6 | 5  | 5    | 16     |

Conditionally branch to the instruction at the label if the contents of register Rsrc1 are less than Src2:

blt Rsrc1, Src2, label bltu Rsrc1, Src2, label Branch on Less Than <sup>†</sup> Branch on Less Than Unsigned <sup>†</sup>

Conditionally branch to the instruction at the label if the contents of Rs are less than 0:

| blt | tz Rs, label |    |   | Branch on Less Than Zero |

|-----|--------------|----|---|--------------------------|

|     | 1            | Rs | 0 | Offset                   |

|     | 6            | 5  | 5 | 16                       |

Conditionally branch to the instruction at the label if the contents of register Rsrc1 are not equal to Src2:

bne Rs, Rt, label

Branch on Not Equal

| 5 | Rs | $\operatorname{Rt}$ | Offset |

|---|----|---------------------|--------|

| 6 | 5  | 5                   | 16     |

Conditionally branch to the instruction at the label if the contents of Rsrc are not equal to 0:

bnez Rsrc, label

Branch on Not Equal Zero<sup>†</sup>

Unconditionally jump to the instruction at Target:

j label

Jump

| 2 | Target |

|---|--------|

| 6 | 26     |

Unconditionally jump to the instruction at Target. Save the address of the next instruction in register 31:

jal label

Jump and Link

Unconditionally jump to the instruction whose address is in register Rs. Save the address of the next instruction in register Rd (or in register 31, if Rd is omitted):

| ja | lr [Rd,] Rs |    |   |    | Jump a | and Link Registe | r |

|----|-------------|----|---|----|--------|------------------|---|

|    | 0           | Rs | 0 | Rd | 0      | 9                |   |

|    | 6           | 5  | 5 | 5  | 5      | 6                |   |

Unconditionally jump to the instruction whose address is in register Rs:

jr Rs

Jump Register

| ĺ | 0 | Rs | 0  | 8 | ] |

|---|---|----|----|---|---|

|   | 6 | 5  | 16 | 5 | 1 |

### Load Instructions

Load computed *address*, not the contents of the location, into register Rdest:

la Rdest, address

Load Address <sup>†</sup>

Load Byte

Load the byte at *address* (or at Offset + contents of register Base) into register Rt. The byte is sign-extended by the lb, but not the lbu, instruction:

lb Rt, address|Offset(Base)

| 0x20 | Base | Rt | Offset |

|------|------|----|--------|

| 6    | 5    | 5  | 16     |

lbu Rt, address|Offset(Base)

Load Unsigned Byte

Load the 64-bit quantity at *address* into registers Rdest and Rdest + 1:

ld Rdest, address

Load Double-Word <sup>†</sup>

Load the 16-bit quantity (halfword) at *address* (or at Offset + contents of register Base) into register Rt. The halfword is sign-extended by the lh, but not the lhu, instruction:

| lh | Rt, address Offset(Base)<br>0x21     Base     Rt       6     5     5       a Rt, address Offset(Base)     0x25     Base     Rt       6     5     5       ad the 16-bit immediate into the rest       i Rt, Imm |                    |             | Load Halfword                                   |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|-------------------------------------------------|

|    | 0x21                                                                                                                                                                                                           | Base               | Rt          | Offset                                          |

|    | 6                                                                                                                                                                                                              | 5                  | 5           | 16                                              |

| lh | u Rt, addres                                                                                                                                                                                                   | s Offset(          | Base)       | Load Unsigned Halfword                          |

|    | 0x25                                                                                                                                                                                                           | Base               | Rt          | Offset                                          |

|    | 6                                                                                                                                                                                                              | 5                  | 5           | 16                                              |

| Lo | ad the 16-bit                                                                                                                                                                                                  | <i>immediate</i> i | into the mo | st significant 16 bits of register Rt:          |

| lu | i Rt, Imm                                                                                                                                                                                                      |                    |             | Load Upper Immediate                            |

|    | 15                                                                                                                                                                                                             | 0                  | Rt          | Imm                                             |

|    | 6                                                                                                                                                                                                              | 5                  | 5           | 16                                              |

| lw | Rt, address                                                                                                                                                                                                    | Base               | ase)<br>Rt  | Load Word Offset                                |

|    | 0x23                                                                                                                                                                                                           | Base               | Rt          | Offset                                          |

|    | 6                                                                                                                                                                                                              | 5                  | 5           | 16                                              |

|    | ad the word at<br>of coprocesso                                                                                                                                                                                |                    | r at Offset | + contents of register Base) into register      |

| lw | c $z$ Rt, addre                                                                                                                                                                                                | ess Offset         | (Base)      | Load Word Coprocessor                           |

|    | 0x3z                                                                                                                                                                                                           | Base               | Rt          | Offset                                          |

|    | 6                                                                                                                                                                                                              | 5                  | 5           | 16                                              |

|    | ad the left (rig<br>sister <b>Rdest</b> :                                                                                                                                                                      | ght) bytes fr      | com the wor | d at the possibly-unaligned <i>address</i> into |

| lw | l Rdest, add                                                                                                                                                                                                   | lress              |             | Load Word Left                                  |

|    |                                                                                                                                                                                                                |                    |             |                                                 |

| lwr Rdest, address Load Word |      |    |    |        |  |  |

|------------------------------|------|----|----|--------|--|--|

|                              | 0x23 | Rs | Rt | Offset |  |  |

|                              | 6    | 5  | 5  | 16     |  |  |

Load the 16-bit quantity (halfword) at the possibly-unaligned *address* into register Rdest. The halfword is sign-extended by the ulh, but not the ulhu, instruction:

ulh Rdest, addressUnaligned Load Halfword †ulhu Rdest, addressUnaligned Load Halfword Unsigned †

Load the 32-bit quantity (word) at the possibly-unaligned address into register Rdest:

ulw Rdest, address

Unaligned Load Word<sup>†</sup>

### Store Instructions

Store the low byte from register Rt at *address*:

sb Rt, address

Store Byte

0x28 Rs

Rt

Offset

6

5

5

16

Store the 64-bit quantity in registers Rsrc and Rsrc + 1 at address:

sd Rsrc, address

Store Double-Word †

Store the low halfword from register Rt at *address*:

| sh Rt, address Store H |      |    |    |        |  |  |

|------------------------|------|----|----|--------|--|--|

|                        | 0x29 | Rs | Rt | Offset |  |  |

|                        | 6    | 5  | 5  | 16     |  |  |

Store the word from register Rt at *address*:

| sw  | Rt, address      | 3            |                     | Store Word                                      |  |  |

|-----|------------------|--------------|---------------------|-------------------------------------------------|--|--|

|     | 0x2b             | Rs           | Rt                  | Offset                                          |  |  |

|     | 6                | 5            | 5                   | 16                                              |  |  |

|     |                  |              |                     |                                                 |  |  |

| Sto | ore the word f   | rom register | r Rt of copr        | ocessor $z$ at <i>address</i> :                 |  |  |

| swo | z Rt, addre      | ess          |                     | Store Word Coprocessor                          |  |  |

|     | 0x3(1-z)         | Rs           | $\operatorname{Rt}$ | Offset                                          |  |  |

|     | 6                | 5            | 5                   | 16                                              |  |  |

|     |                  |              |                     |                                                 |  |  |

| Sto | ore the left (ri | ght) bytes f | rom registe         | r Rt at the possibly-unaligned <i>address</i> : |  |  |

|     |                  | 0 - / - /    |                     | r i j i j i j i j i j i j i j i j i j i         |  |  |

| sw] | L Rt, addres     | SS           |                     | Store Word Left                                 |  |  |

|     | 0x2a             | Rs           | Rt                  | Offset                                          |  |  |

|     | 6                | 5            | 5                   | 16                                              |  |  |

| swi | r Rt, addres     | s            |                     | Store Word Right                                |  |  |

|     | 0x2e             | Rs           | Rt                  | Offset                                          |  |  |

|     | 6                | 5            | 5                   | 16                                              |  |  |

|     |                  |              |                     |                                                 |  |  |

| Ste | ore the low ha   | lfword from  | register Rs         | rc at the possibly-unaligned <i>address</i> :   |  |  |

| usł | n Rsrc, addr     | ress         |                     | Unaligned Store Halfword $^{\dagger}$           |  |  |

|     |                  |              |                     |                                                 |  |  |

| Sto | ore the word f   | rom register | r <b>Rsrc</b> at th | e possibly-unaligned <i>address</i> :           |  |  |

| usi | v Rsrc, addr     | ress         |                     | Unaligned Store Word $^{\dagger}$               |  |  |

|     |                  |              |                     |                                                 |  |  |

# **Data Movement Instructions**

Move the contents of  $\tt Rsrc$  to  $\tt Rdest:$

move Rdest, Rsrc

Move  $^{\dagger}$

The multiply and divide unit produces its result in two additional registers, hi and lo. The following instructions move values to and from these registers. The multiply, divide, and remainder instructions described above are pseudoinstructions that make it appear as if this unit operates on the general registers and detect error conditions such as divide by zero or overflow.

Move the contents of the hi (lo) register to register Rd: mfhi Rd Move From hi 0 0  $\operatorname{Rd}$ 0 0x10 6 10 6 55Move From lo mflo Rd 0 0x12 Rd 0 0 6 10 5 56 Move the contents of register Rs to the hi (lo) register: mthi Rs Move To hi 0 0x11 0  $\mathbf{Rs}$ 6 5 156 Move To lo mtlo Rs 0 0x130 Rs 6 6 515

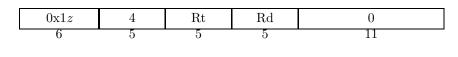

Coprocessors have their own register sets. The following instructions move values between these registers and the CPU's registers.

Move the contents of coprocessor z's register Rd to CPU register Rt:

| mf | mfcz Rt, Rd Move From Coprocessor z |   |    |    |    |  |  |  |

|----|-------------------------------------|---|----|----|----|--|--|--|

|    | 0 x 1 z                             | 0 | Rt | Rd | 0  |  |  |  |

|    | 6                                   | 5 | 5  | 5  | 11 |  |  |  |

Move the contents of floating point registers FRsrc1 and FRsrc1 + 1 to CPU registers Rdest and Rdest + 1:

mfc1.d Rdest, FRsrc1

Move Double From Coprocessor 1<sup>†</sup>

Move the contents of CPU register Rt to coprocessor z's register Rd:

mtcz Rt, Rd

Move To Coprocessor z

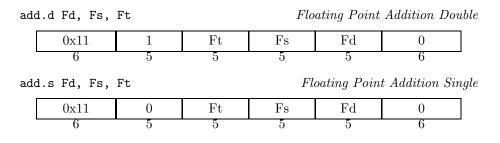

### **Floating Point Instructions**

The MIPS has a floating point coprocessor (numbered 1) that operates on single precision (32-bit) and double precision (64-bit) floating point numbers. This coprocessor has its own registers, which are numbered **\$f0-\$f31**. Because these registers are only 32-bits wide, two of them are required to hold doubles. To simplify matters, floating point operations only use even-numbered registers—including instructions that operate on single floats.

Values are moved in or out of these registers one word (32-bits) at a time by the lwc1, swc1, mtc1, and mfc1 instructions described above or by the l.s, l.d, s.s, and s.d pseudoinstructions described below. The flag set by floating point comparison operations is read by the CPU with its bc1t and bc1f instructions.

In the real instructions below, Fs and Fd are floating-point registers. In the pseudoinstructions, FRdest, FRsrc1, FRsrc2, and FRsrc are floating point registers (e.g., \$f2).

Compute the absolute value of the floating float double (single) in register Fs and put it in register Fd:

| abs.d Fd, Fs                                      |      |   |   | Floating Point Absolute Value Double |               |   |  |

|---------------------------------------------------|------|---|---|--------------------------------------|---------------|---|--|

|                                                   | 0x11 | 1 | 0 | Fs                                   | Fd            | 5 |  |

|                                                   | 6    | 5 | 5 | 5                                    | 5             | 6 |  |

| abs.s Fd, Fs Floating Point Absolute Value Single |      |   |   |                                      |               |   |  |

|                                                   | 0 11 | 0 | 0 | Г                                    | <b>D</b> 1    | - |  |

|                                                   | 0x11 | 0 | 0 | Fs                                   | $\mathrm{Fd}$ | Э |  |

Compute the sum of the floating float doubles (singles) in registers Fs and Ft and put it in register Fd:

Compare the floating point double in register Fs against the one in Ft and set the floating point condition flag FC true if they are equal:

| c.eq.d Fs, Ft |                     |   |                     |               | $Com_{2}$ | ıble          |           |      |

|---------------|---------------------|---|---------------------|---------------|-----------|---------------|-----------|------|

|               | 0x11                | 1 | $\operatorname{Ft}$ | $\mathbf{Fs}$ | Fd        | $\mathbf{FC}$ | 2         |      |

|               | 6                   | 5 | 5                   | 5             | 5         | 2             | 4         | -    |

|               |                     |   |                     |               |           |               |           |      |

| с.            | eq.s Fs, Ft         |   |                     |               | Com       | npare E       | 'qual Sir | ngle |

| с.            | eq.s Fs, Ft<br>0x11 | 0 | Ft                  | Fs            | Con<br>Fd | pare E        | qual Sir  | ngle |

Compare the floating point double in register Fs against the one in Ft and set the floating point condition flag true if the first is less than or equal to the second:

c.le.d Fs, Ft

Compare Less Than Equal Double

|    | 0x11        | 1 | $\operatorname{Ft}$ | $\mathbf{Fs}$ | 0         | $\mathbf{FC}$ | 2         |     |

|----|-------------|---|---------------------|---------------|-----------|---------------|-----------|-----|

|    | 6           | 5 | 5                   | 5             | 5         | 2             | 4         |     |

| с. | le.s Fs, Ft |   |                     | $Com_{f}$     | pare Less | Than          | Equal Sin | gle |

| 0x11  | 0 | $\operatorname{Ft}$ | $\mathbf{Fs}$ | 0 | $\mathbf{FC}$ | 2 |

|-------|---|---------------------|---------------|---|---------------|---|

| <br>6 | 5 | 5                   | 5             | 5 | 2             | 4 |

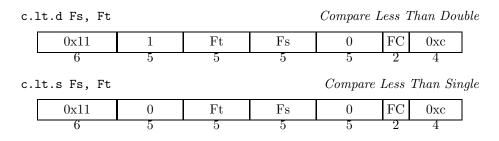

Compare the floating point double in register Fs against the one in Ft and set the condition flag true if the first is less than the second:

Convert the single precision floating point number or integer in register Fs to a double precision number and put it in register Fd:

| .d.s Fd, Fs |                          |                    |                                  | Convert Single to Double              |                                                                                                                                                                          |                                                                                                                                                                               |  |

|-------------|--------------------------|--------------------|----------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x11        | 1                        | 0                  | Fs                               | Fd                                    | 0x21                                                                                                                                                                     | ]                                                                                                                                                                             |  |

| 6           | 5                        | 5                  | 5                                | 5                                     | 6                                                                                                                                                                        | -                                                                                                                                                                             |  |

| .d.w Fd, Fs |                          |                    |                                  | Convert 1                             | Integer to Do                                                                                                                                                            | uble                                                                                                                                                                          |  |

| 0x11        | 0                        | 0                  | Fs                               | Fd                                    | 0x21                                                                                                                                                                     | ]                                                                                                                                                                             |  |

| 6           | 5                        | 5                  | 5                                | 5                                     | 6                                                                                                                                                                        |                                                                                                                                                                               |  |

|             | 0x11<br>6<br>.d.w Fd, Fs | 6 5<br>.d.w Fd, Fs | 0x11 1 0<br>6 5 5<br>.d.w Fd, Fs | 0x11 1 0 Fs<br>6 5 5 5<br>.d.w Fd, Fs | 0x11         1         0         Fs         Fd           6         5         5         5         5           .d.w Fd, Fs         Convert         Convert         Convert | 0x11         1         0         Fs         Fd         0x21           6         5         5         5         5         6           .d.w Fd, Fs         Convert Integer to Do |  |

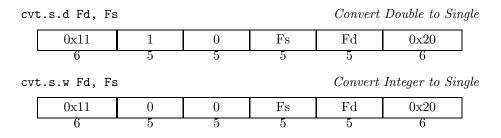

Convert the double precision floating point number or integer in register Fs to a single precision number and put it in register Fd:

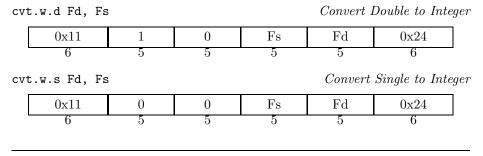

Convert the double or single precision floating point number in register Fs to an integer and put it in register Fd:

Compute the quotient of the floating float doubles (singles) in registers Fs and Ft and put it in register Fd:

| di  | 7.d Fd, Fs,                                     | Ft           |                     | Floating Point Divide Double |              |                                                                          |  |

|-----|-------------------------------------------------|--------------|---------------------|------------------------------|--------------|--------------------------------------------------------------------------|--|

|     | 0x11                                            | 1            | Ft                  | Fs                           | Fd           | 3                                                                        |  |

|     | 6                                               | 5            | 5                   | 5                            | 5            | 6                                                                        |  |

| di  | 7.s Fd, Fs,                                     | Ft           |                     |                              | Floating Po  | int Divide Single                                                        |  |

|     | 0x11                                            | 0            | $\operatorname{Ft}$ | $\mathbf{Fs}$                | Fd           | 3                                                                        |  |

|     | 6                                               | 5            | 5                   | 5                            | 5            | 6                                                                        |  |

| 1.0 | ad the floating<br>1 FRdest, ad<br>5 FRdest, ad | ldress       | le (single) a       | L                            | oad Floatin  | r FRdest:<br>g Point Double <sup>†</sup><br>ng Point Single <sup>†</sup> |  |

| Mo  | we the floatin                                  | g float doul | ble (single)        | from registe                 | r Fs to regi | ster Fd:                                                                 |  |

| mov | 7.d Fd, Fs                                      |              |                     |                              | Move Float   | ing Point Double                                                         |  |

|     | $0 \times 11$                                   | 1            | Ο                   | $\mathbf{F}_{\mathbf{c}}$    | Fd           | 6                                                                        |  |

|     | 0x11       | 1 | 0 | $\mathbf{Fs}$ | Fd        | 6              |     |

|-----|------------|---|---|---------------|-----------|----------------|-----|

|     | 6          | 5 | 5 | 5             | 5         | 6              |     |

| mov | v.s Fd, Fs |   |   |               | Move Floa | ting Point Sin | gle |

|     | 0x11       | 0 | 0 | $\mathbf{Fs}$ | Fd        | 6              |     |

|     | 6          | 5 | 5 | 5             | 5         | 6              |     |

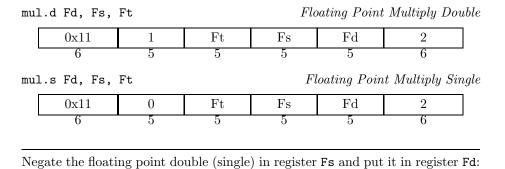

Compute the product of the floating float doubles (singles) in registers Fs and Ft and put it in register Fd:

Store the floating float double (single) in register FRdest at address: Store the floating float double (single) in register FRdest at address:

| s.d | FRdest, | address |

|-----|---------|---------|

| s.s | FRdest, | address |

Store Floating Point Double<sup>†</sup> Store Floating Point Single<sup>†</sup>

Compute the difference of the floating float doubles (singles) in registers Fs and Ft and put it in register Fd:

| sul                                            | sub.d Fd, Fs, FtFloating Point Subtract Double |   |                     |               |    |   |

|------------------------------------------------|------------------------------------------------|---|---------------------|---------------|----|---|

|                                                | 0x11                                           | 1 | $\operatorname{Ft}$ | $\mathbf{Fs}$ | Fd | 1 |

|                                                | 6                                              | 5 | 5                   | 5             | 5  | 6 |

| sub.s Fd, Fs, FtFloating Point Subtract Single |                                                |   |                     |               |    |   |

|                                                | 0x11                                           | 0 | Ft                  | Fs            | Fd | 1 |

|                                                | -                                              | - |                     |               |    |   |

### **Exception and Trap Instructions**

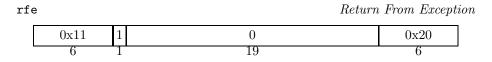

Restore the Status register:

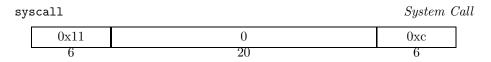

Register v0 contains the number of the system call (see Table  $\ref{thm:see}$  provided by SPIM:

Cause exception n. Exception 1 is reserved for the debugger:

| break | n |

|-------|---|

|-------|---|

Break

Do nothing:

nop

No operation

0

0

0

0

0

6

5

5

5

6