## Architetture - canale AD+PR

Scritto di teoria del 25 giugno 2010

| Nome:      |       |

|------------|-------|

| Matricola: | <br>_ |

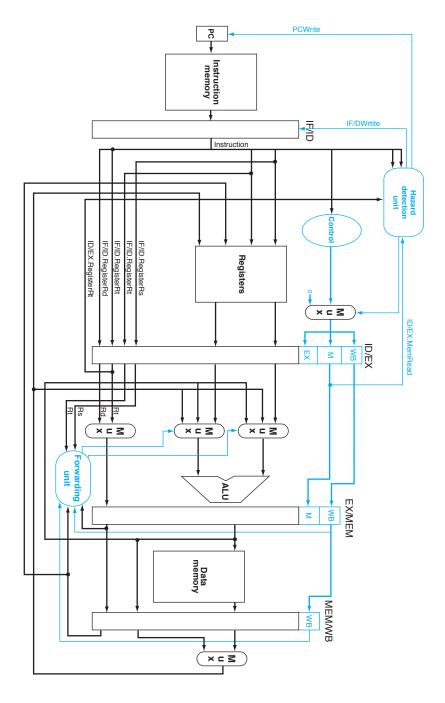

Esercizio 1. Considerate l'architettura MIPS con pipeline in Figura 1 (è quella vista a lezione) e rispondete a queste due domande:

- 1. quanti cicli di clock sono necessari per completare l'esecuzione del seguente frammento di codice?

- 2. Quanti cicli di clock sarebbero stati necessari se non fosse stato inventato il forwarding?

Tenete conto delle seguenti cose:

- l'esecuzione termina quando l'ultima istruzione *esce* dalla pipeline, per semplicità, considerate che *tutte* le istruzioni eseguano tutti e cinque gli stadi della pipeline;

- se nel blocco registri scrivete e leggete contemporaneamente (durante lo stesso ciclo di clock) lo stesso registro, il valore letto è quello che state scrivendo (quello nuovo).

Fate vedere la correttezza della vostra risposta disegnando lo schema della pipeline.

lw \$s1, 4(\$s0)

lw \$s2, 0(\$s0)

sw \$s0, 12(\$s2)

sub \$s3, \$s7, \$s0

add \$s7, \$s3, \$s3

lw \$s7, 0(\$s5)

lw \$s5,4(\$s7)

Figure 1: Architettura con pipeline.

Esercizio 2. Ecco una serie di accessi a word di 32 bit in memoria: 8, 12, 44, 64, 84, 52, 256, 192, 76, 44, 12, 88, 16, 300, 44. Gli indirizzi sono a byte! Assumete di avere una cache *one-way associative* con 4 blocchi di 8 word, inizialmente vuota. Indicate quali accessi sono miss e quali hit.

Sapendo che gli indirizzi sono di 32 bit, di quanti bit è formata la cache?

Esercizio 3. La scorsa domenica siete andati a trovare il vecchio zio Gianni. Purtroppo, non sapete come, è venuto a sapere che vi siete iscritti a Informatica alla Sapienza! Adesso chissà cosa si inventa. Infatti: zio Gianni prende un pezzetto di carta e scrive il seguente programmino:

```

long int i;

long int s;

s=0;

for(i=0; i<2048; i++)

s+=a[i];</pre>

```

Poi vi chiede, sapendo che a è un vettore di 2048 interi, sapendo che la cache è four-way associative con 1024 set e blocchi da 128 word, che la memoria virtuale è paginata con pagine da 4Kb, che il programma e il vettore sono allineati a un multiplo di 4K e che sono su pagine di memoria virtuale diverse, e assumendo che i e s sono mappati su registri:

- 1. potete stimare quanti sono i miss sulla cache per l'accesso al vettore?

- 2. potete stimare quanti sono i miss sulla TLB in totale?

- 3. che succederebbe alle prestazioni di questo programma se non ci fosse una TLB?

Zio Gianni vi guarda spaesati e pensa: l'Università non è più quella di una volta.