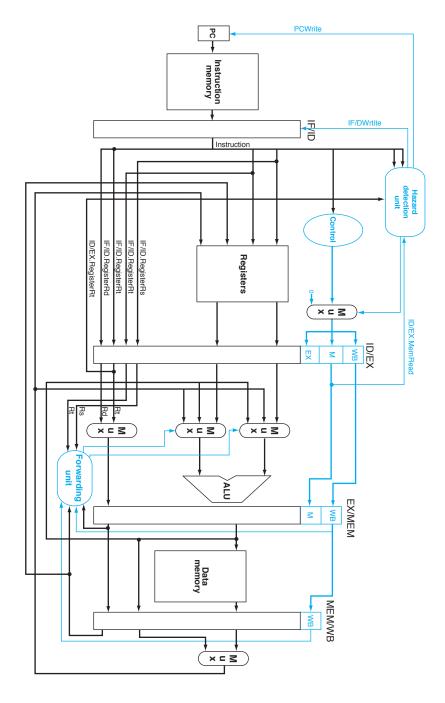

Esercizio 1. Considerate l'architettura MIPS con pipeline in Figura 1. Quanti cicli di clock sono necessari per completare l'esecuzione del seguente frammento di codice? (L'esecuzione termina quando l'ultima istruzione esce dalla pipeline.) Fate vedere la correttezza della vostra risposta disegnando lo schema della pipeline.

```

lw $s1, 12($s1)

lw $s1, 8($s1)

add $t0, $s1, $t1

subi $t2, $t2, 1

```

Esiste un modo per riordinare questo codice in modo da renderlo più veloce? Di quanto?

Figure 1: Architettura con pipeline.

Esercizio 2. Ecco una serie di accessi a word di 32 bit in memoria: 8, 12, 44, 64, 84, 52, 256, 192, 76, 44, 12, 88, 16, 108, 24 e 44. Assumete di avere una cache one-way con 4 blocchi di 4 word, inizialmente vuota. Indicate quali accessi sono miss e quali hit.