# Architettura degli Elaboratori Lez. 1 – Introduzione al corso

Prof. Andrea Sterbini - sterbini@di.uniroma1.it

#### Introduzione al corso

#### Libro di testo:

David A. Patterson,

John L. Hennessy,

"STRUTTURA E PROGETTO DEI CALCOLATORI",

Zanichelli

#### Esame:

- Prova scritta di teoria

- Prova pratica di Assembler (in laboratorio)

- Orale (ammessi se le altre prove sono superate)

#### Argomenti del corso:

- Introduzione storica e struttura di una CPU

- L'assembler MIPS

- Progetto della CPU MIPS ad un colpo di clock

- Introduzione alla Pipeline

- Progetto della CPU MIPS con pipeline

- Gestione degli hazard ed eccezioni

- ▶ Parallelismo

- Gerarchia di memoria e Cache

- Memoria Virtuale e protezione

## GENERAZIONE "-100"

- I primi esempi di macchina **meccanica**

- ▶ 150-100 AC: macchina di **Antikythera** per predire le eclissi

Meccanismi "programmabili" a camme e pistoni (p.es. barca con banda musicale)

- il "Moro" giocatore di scacchi (che conteneva un nano)

- Lo scrivano, il disegnatore ed il musicista di Drosz

- ▶ Il cavaliere meccanico in armatura (Leonardo da Vinci)

- ... molti altri

### GENERAZIONE "0"

- ▶ 1642: Blaise Pascal:

- ▶ la Pascalina calcolatrice meccanica

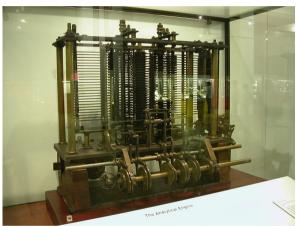

- ▶ 1833: Charles Babbage Analytical Engine

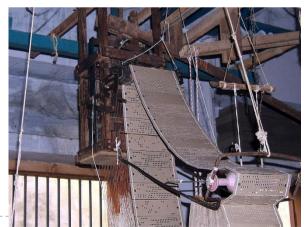

- ► **1839**: Telaio automatico **Jacquard** («programmabile» a schede perforate!)

- I primi computer digitali

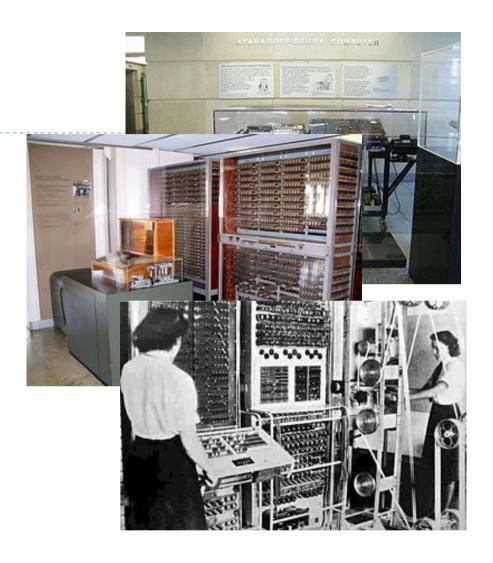

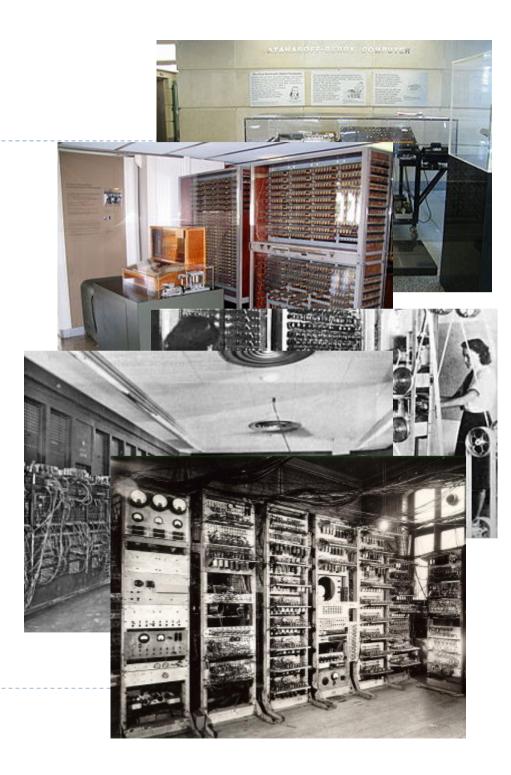

- ▶1937 ABC (US)

- Atanasoff-Berry Computer

- X risolvere sistemi di equazioni lineari

- I primi computer digitali

- ▶1937 ABC (US)

- Atanasoff-Berry Computer

- X risolvere sistemi di equazioni lineari

- ▶1941 Z3 (Konrad Zuse)

- >2200 relè (elettromeccanico)

- Programmato con nastro perforato

- I primi computer digitali

- ▶1937 ABC (US)

- Atanasoff-Berry Computer

- X risolvere sistemi di equazioni lineari

- ▶1941 Z3 (Konrad Zuse)

- >2200 relè (elettromeccanico)

- Programmato con nastro perforato

- ▶1944 Colossus (UK)

- >2400 Valvole

- Cablato (Programmato collegando tra loro le parti a seconda del compito da svolgere)

- Per decodificare i messaggi nazisti

- I primi computer digitali

- ▶1937 ABC (US)

- ▶ Atanasoff-Berry Computer

- X risolvere sistemi di equazioni lineari

#### ▶1941 Z3 (Konrad Zuse)

- ▶2200 relè (elettromeccanico)

- Programmato con nastro perforato

#### ▶1944 Colossus (UK)

- >2400 Valvole

- ▶ Cablato (Programmato collegando tra loro le parti a seconda del compito da svolgere)

- Per decodificare i messaggi nazisti

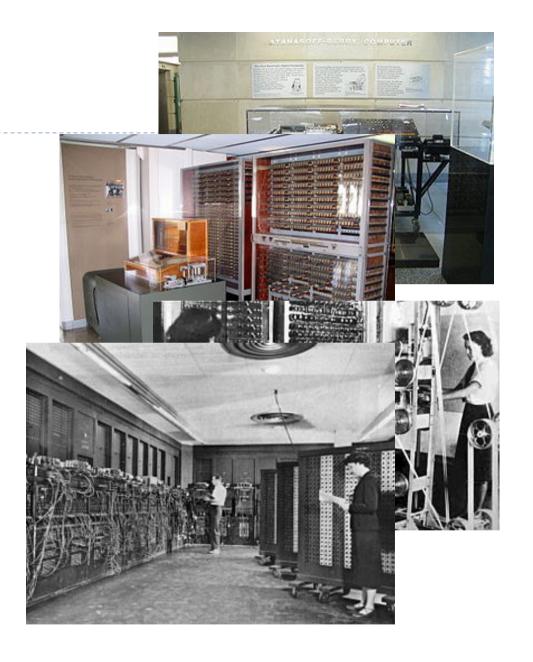

#### ▶1946 ENIAC (US)

▶ I 8000 Valvole, Cablato, General purpose

- I primi computer digitali

- ▶1937 ABC (US)

- ▶ Atanasoff-Berry Computer

- X risolvere sistemi di equazioni lineari

- ▶1941 Z3 (Konrad Zuse)

- ▶2200 relè (elettromeccanico)

- Programmato con nastro perforato

- ▶1944 Colossus (UK)

- >2400 Valvole

- Cablato (Programmato collegando tra loro le parti a seconda del compito da svolgere)

- Per decodificare i messaggi nazisti

- ▶1946 ENIAC (US)

- ▶ I 8000 Valvole, Cablato, General purpose

- ▶1948 Mark I (UK)

- bll primo computer a programma memorizzato

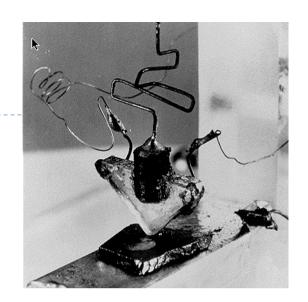

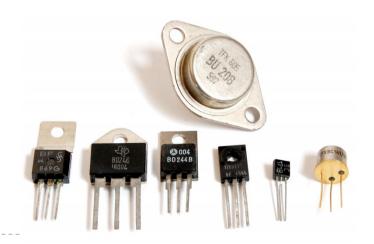

- ▶ 1947: Introduzione dei transistor

- Piccoli, robusti, veloci, consumano poco (le valvole si rompevano o bruciavano)

- ▶ NCR, RCA, IBM: i primi computer commerciali

- ▶ **ALU** complesse

- Trasferimento Diretto in Memoria (**DMA**)

- Linguaggi di alto livello

- **FORTRAN:** calcoli numerici

- ► **ALGOL:** simulazioni (a oggetti!)

- **COBOL:** calcoli finanziari

- ▶ **DEC** sviluppa i primi Minicomputer

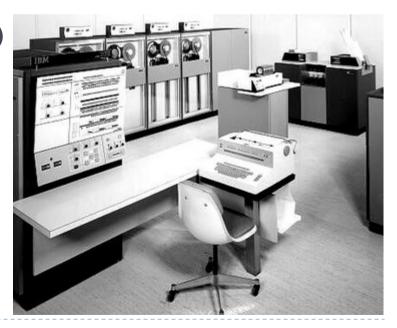

- **1964:**

- ▶ IBM serie 360: compatibili "verso l'alto"

- Stesse istruzioni (+ istr. avanzate)

- Stesso Sistema Op. (+ funz. avanzate)

- Velocità crescente

- Memoria crescente

- Parallelismo crescente

- Molto costoso (100K\$)

- **1964:**

- ▶ IBM serie 360: compatibili "verso l'alto"

- Stesse istruzioni (+ istr. avanzate)

- Stesso Sistema Op. (+ funz. avanza<del>te)</del>

- Velocità crescente

- Memoria crescente

- Parallelismo crescente

- Molto costoso (100K\$)

| .t <del>e)</del>     | da       | a         |

|----------------------|----------|-----------|

| RAM                  | 64 Kbyte | 512 Kbyte |

| CLOCK                | I MHz    | 5 MHz     |

| Banda<br>CPU/ME<br>M | 0,5 MB/s | I6 MB/s   |

- **1964:**

- ▶ IBM serie 360: compatibili "verso l'alto"

- Stesse istruzioni (+ istr. avanzate)

- Stesso Sistema Op. (+ funz. avanzate)

- Velocità crescente

- Memoria crescente

- Parallelismo crescente

- Molto costoso (100K\$)

- ▶ 1958: Introduzione dei circuiti integrati

- **1964:**

- ▶ **IBM serie 360**: compatibili "verso l'alto"

- Stesse istruzioni (+ istr. avanzate)

- Stesso Sistema Op. (+ funz. avanzate)

- Velocità crescente

- Memoria crescente

- Parallelismo crescente

- Molto costoso (100K\$)

- **DECPDP-8**:poco costoso (16K\$ -> 2500\$)

- **Bus** di interconnessione **standardizzato**

- <sup>7</sup> Facilità di espansione (produttori OEM)

C4004 N5832

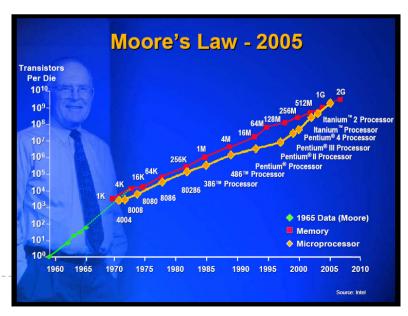

- ► Circuiti integrati su larga e larghissima scala (**VLSI**)

- **1971:**

- ▶ Intel 4004: l° processore integrato (a 4 bit)

- Memorie integrate

- Legge (osservazione) di Moore: "la densità di transistor raddoppia ogni 12-18 mesi"

- ▶ Ne segue che:

- > => Il costo di produzione resta uguale

- => Il prezzo per componente decresce

- > => La distanza tra componenti diminuisce

- > => La velocità aumenta

- > => L'energia ed il calore diminuiscono

- > => L'affidabilità aumenta

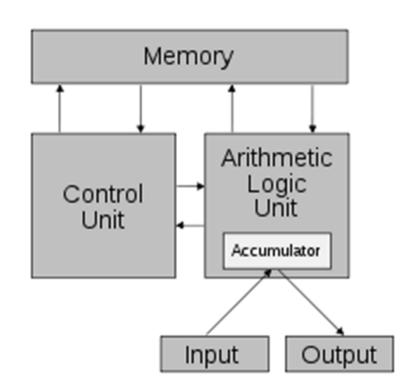

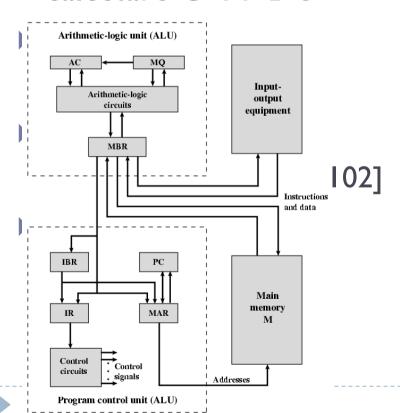

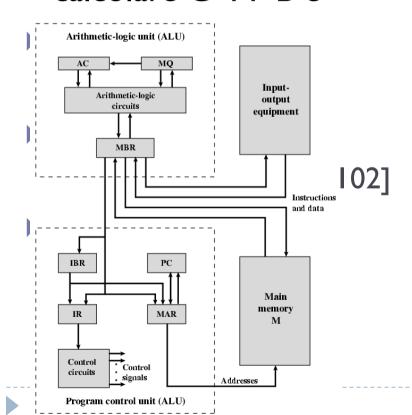

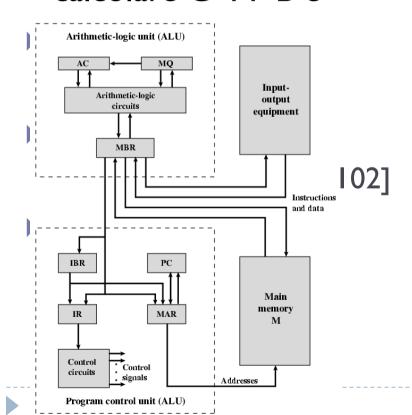

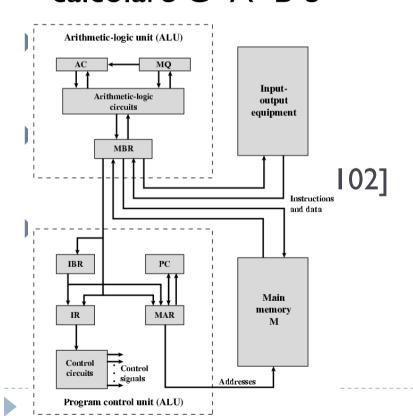

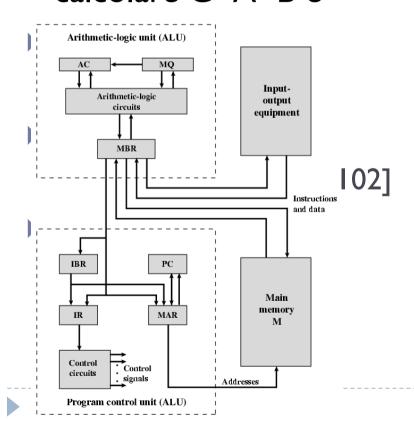

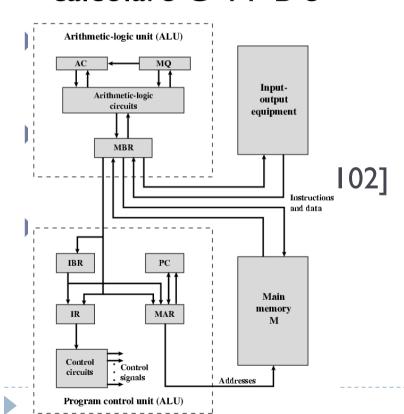

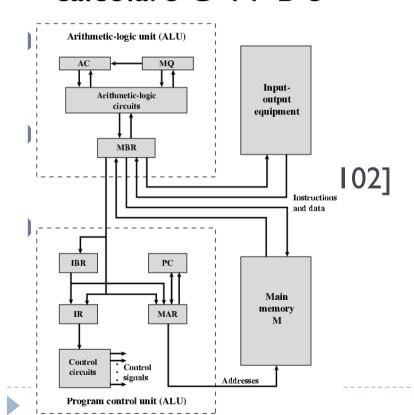

# Architettura di Von Neumann a programma memorizzato

- ▶Un computer è diviso in:

- **▶** Memoria

- dati e programmi

- **CPU** (CU + ALU + registri)

- **Bus** di comunicazione tra le diverse parti

- Periferiche di I/O (tastiera, schermo, stampante, scheda di rete eccetera)

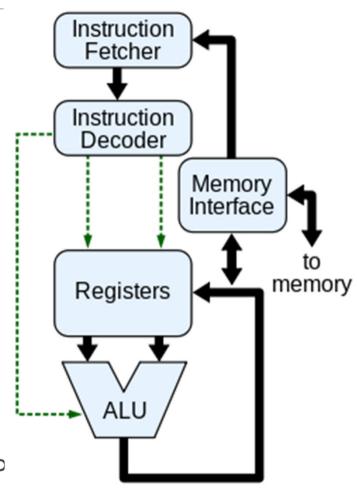

### La CPU

#### La Central Processing Unit è formata da:

- La Unità di elaborazione Aritmetico / Logica (ALU)

- ▶fa solo calcoli

- NON ha uno stato interno

#### ▶ | registri

- A uso generale e speciale,

- per manipolare istruzioni, indirizzi, dati, risultati

- Il **bus** di comunicazione con la **M**emoria

- Il **bus** di comunicazione con le periferiche (non necessario col memory mapping)

- La Unità di Controllo che coordina il tutto (Instruction Decoder nella figura)

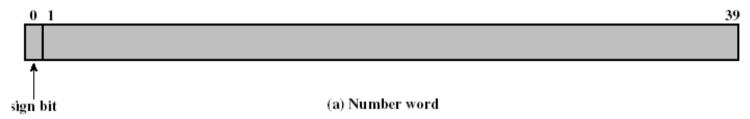

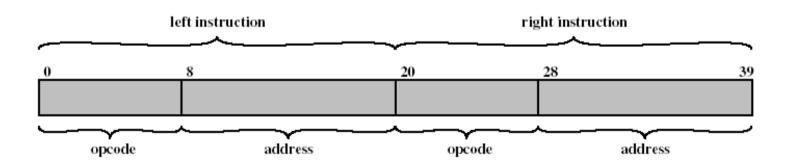

# Esempio: la IAS machine

- ▶ 1951: Institute for Advanced Studies Princeton

- Memoria di 1000 word da 40 bit (ovvero 5 Kbyte totali!!!)

- >dati: solo interi nella rappresentazione in Complemento a 2

- ▶istruzioni: 2 istruzioni per ciascuna word

(b) Instruction word

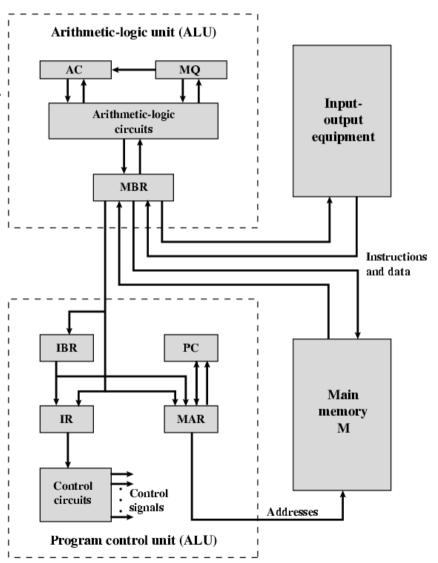

### La CPU della IAS machine

► MBR: Memory Buffer Register riceve/manda il dato dalla/alla mer

▶MAR: Memory Address Register indica l'indirizzo in memoria

▶PC: Program Counter indirizzo dell'istr. da eseguire

▶ IR: Instruction Register riceve l'istruzione da eseguire

▶**IBR**: Instruction Buffer Register 2° istruzione della word

▶AC: Accumulatore per i risultati parziali dei calcoli

▶ MQ: Multiplier Quotient per i risultati parziali dei calcoli

#### Istruzioni di trasferimento

▶ LOAD caricamento da memoria con operazioni semplici (ABS, NEG, ADD, SUB)

(con oppure senza il valore precedente di AC)

AC <- AC < operazione > Memory (Address)

**AC <- <operazione> Memory(Address)**

LDMQ caricamento nel registro MQ

MQ <- Memory(Address)

ST memorizzazione di AC come dato

Memory(Address) <- AC

AMODL memorizzazione di AC come indirizzo in una istruzione

(parte bassa della word)

Memory(Address)[bits 0:11] <- AC[bits 0:11]

**AMODH** memorizzazione di AC come indirizzo in una istruzione

(parte alta della word)

Memory(Address) [bits 20:31] <- AC[bits 0:11]

#### Istruzioni di salto

#### Salti NON condizionati

**UBL** salto <u>incondizionato</u> all'istruzione (parte bassa della parola)

PC <- Address; offsetPC <- 0

**UBH** salto <u>incondizionato</u> all'istruzione (parte alta della parola)

PC <- Address; offsetPC <- I

Salti condizionati

**CBL** salto <u>condizionato</u> all'istruzione (parte alta della parola)

if AC >= 0 then PC <- Address; offsetPC <- 0

**CBH** salto <u>condizionato</u> all'istruzione (parte alta della parola)

if AC >= 0 then PC <- Address; offsetPC <- I

# Operazioni aritmetiche (e I/O)

**MUL** prodotto

AC,MQ <- AC \* Mem(Address)

**DIV** divisione e resto

AC <- AC / Mem(Address); MQ <- AC % Mem(Address)

▶ **LSHIFT** shift a sinistra (ovvero prodotto per 2^X)

AC,MQ <- AC,MQ << X

**RSHIFT** shift a destra con estensione del segno (ovvero divisione per 2<sup>X</sup>)

AC,MQ <- AC,MQ >> X

**MOVE** spostamenti da MQ ad AC con le (8) operazioni semplici

(ADD, SUB, ABS, NEG ...)

AC <- AC < operazione > MQ

trasferimento da e verso le periferiche

- Se A, B e C sono le locazioni 101, 102, 103 in memoria, il codice per calcolare C=A+B è

- LD | 101

AC <- Mem[101]</p>

- ADD 102 AC <- AC+Mem[102]

- ► SD 103 Mem[103] <- AC

Esecuzione delle istruzioni

Se A, B e C sono le locazioni 101, 102, 103 in memoria, il codice per calcolare C=A+B è

#### Esecuzione delle istruzioni

Se A, B e C sono le locazioni 101, 102, 103 in memoria, il codice per calcolare C=A+B è

# **Fetch** della istruzione dalla memoria MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

Se A, B e C sono le locazioni 101, 102, 103 in memoria, il codice per calcolare C=A+B è

#### Esecuzione delle istruzioni

Fetch della istruzione dalla memoria

MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

Decodifica della istruzione (da IR)

MAR <- IR.Address; CU <- IR.Opcode

Se A, B e C sono le locazioni 101, 102, 103 in memoria, il codice per calcolare C=A+B è

#### Esecuzione delle istruzioni

Fetch della istruzione dalla memoria

MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

**Decodifica** della istruzione (da IR)

MAR <- IR.Address; CU <- IR.Opcode

Sua esecuzione

AC <- MBR <- Mem[101]

Se A, B e C sono le locazioni 101, 102, 103 in memoria, il codice per calcolare C=A+B è

#### Esecuzione delle istruzioni

Fetch della istruzione dalla memoria

MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

Decodifica della istruzione (da IR)

MAR <- IR.Address; CU <- IR.Opcode

Sua esecuzione

AC <- MBR <- Mem[101]

Fetch della istr. successiva (da IBR)

MAR <- IBR.Address ; CU <- IBR.Op

Se A, B e C sono le locazioni 101, 102, 103 in memoria, il codice per calcolare C=A+B è

#### Esecuzione delle istruzioni

Fetch della istruzione dalla memoria

MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

**Decodifica** della istruzione (da IR)

MAR <- IR.Address; CU <- IR.Opcode

Sua esecuzione

AC <- MBR <- Mem[101]

Fetch della istr. successiva (da IBR)

MAR <- IBR.Address ; CU <- IBR.Op

sua esecuzione

AC <- AC + MBR <- Mem[102]

Se A, B e C sono le locazioni 101, 102, 103 in memoria, il codice per calcolare C=A+B è

#### Esecuzione delle istruzioni

Fetch della istruzione dalla memoria

MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

**Decodifica** della istruzione (da IR)

MAR <- IR.Address; CU <- IR.Opcode

Sua esecuzione

AC <- MBR <- Mem[101]

Fetch della istr. successiva (da IBR)

MAR <- IBR.Address ; CU <- IBR.Op

sua esecuzione

AC <- AC + MBR <- Mem[102]

**Aggiornamento** del PC

PC <- PC + I

Se A, B e C sono le locazioni 101, 102, 103 in memoria, il codice per calcolare C=A+B è

#### Esecuzione delle istruzioni

Fetch della istruzione dalla memoria

MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

**Decodifica** della istruzione (da IR)

MAR <- IR.Address; CU <- IR.Opcode

Sua esecuzione

AC <- MBR <- Mem[101]

Fetch della istr. successiva (da IBR)

MAR <- IBR.Address ; CU <- IBR.Op

sua esecuzione

AC <- AC + MBR <- Mem[102]

**Aggiornamento** del PC

PC <- PC + I

Fetch della istruzione successiva

MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

Se A, B e C sono le locazioni 101, 102, 103 in memoria, il codice per calcolare C=A+B è

#### Esecuzione delle istruzioni

Fetch della istruzione dalla memoria

MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

**Decodifica** della istruzione (da IR)

MAR <- IR.Address; CU <- IR.Opcode

Sua esecuzione

AC <- MBR <- Mem[101]

Fetch della istr. successiva (da IBR)

MAR <- IBR.Address ; CU <- IBR.Op

sua esecuzione

AC <- AC + MBR <- Mem[102]

**Aggiornamento** del PC

PC <- PC + I

Fetch della istruzione successiva

MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

**Decodifica** della istruzione (da IR)

MAR <- IR.Address; CU <- IR.Opcode

Se A, B e C sono le locazioni 101, 102, 103 in memoria, il codice per calcolare C=A+B è

#### Esecuzione delle istruzioni

Fetch della istruzione dalla memoria

MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

**Decodifica** della istruzione (da IR)

MAR <- IR.Address; CU <- IR.Opcode

Sua esecuzione

AC <- MBR <- Mem[101]

Fetch della istr. successiva (da IBR)

MAR <- IBR.Address ; CU <- IBR.Op

sua esecuzione

AC <- AC + MBR <- Mem[102]

**Aggiornamento** del PC

PC <- PC + I

Fetch della istruzione successiva

MAR <- PC

IR, IBR <- MBR <- Mem[MAR]

Decodifica della istruzione (da IR)

MAR <- IR.Address; CU <- IR.Opcode

Sua esecuzione

Mem[103] <- MBR <- AC