### ESAME DI ARCHITETTURA I

### COMPITO A

### Esercizio 1 (16 punti)

Si consideri l'automa di Mealy specificato dalla seguente tabella:

|            | 0    | 1    |

|------------|------|------|

| S0         | S1/0 | S0/0 |

| <b>S</b> 1 | S2/0 | S3/0 |

| S2         | S2/0 | S3/1 |

| <b>S</b> 3 | S1/0 | S0/1 |

| S4         | S1/0 | S0/0 |

| S5         | S2/0 | S3/0 |

- 1) Disegnare l'automa.

- 2) Verificare se l'automa è minimizzabile ed eventualmente disegnare l'automa minimo.

- 3) Disegnare l'automa di Moore equivalente all'automa minimo, se è stato individuato al punto precedente, o all'automa in tabella e **spiegare sinteticamente** come si ottiene.

- 4) Rappresentare su diagramma temporale la sequenza di uscita e gli stati attraversati (nell'automa minimo se esiste, altrimenti nell'automa in tabella) a fronte della sequenza di ingresso: 01000110011.

## Esercizio 2 (14 punti)

Si considerino le funzioni booleane f(x) e g(x), con x espresso da 4 bit nella **rappresentazione in complemento a 2**, definite da:

- f(x) = 1 se e solo se  $x \ge 4$  o x < -4

- g(x) = 1 se e solo x è multiplo di 3

- i) Trovare una espressione POS minimale per f(x) e disegnare un circuito con solo porte NOR.

- ii) Trovare una espressione SOP minimale per g(x) e disegnare un circuito con solo porte NAND.

## ESAME DI ARCHITETTURA I

## COMPITO B

## Esercizio 1 (13 punti)

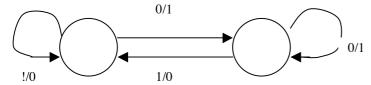

Trasformare il seguente automa di Mealy in un automa di Moore e spiegare sinteticamente, usando un linguaggio formale, come avete ottenuto la conversione.

## Esercizio 2 (17 punti)

Progettare una rete sequenziale con 2 linee di ingresso x e y e una linea di uscita z tale che:

z = 1 ogni volta che sono state ricevute tre coppie xy=00.

Esempio x: **0**1011**00**101111**0**00

y: **0**0101**00**1**0**011**0**10 z: 000000**1**0000000**1**

## ESAME DI ARCHITETTURA I

### Compito C

#### Esercizio 1 (30 punti)

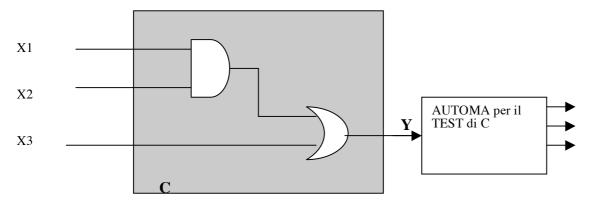

Si consideri il circuito combinatorio C nella parte sinistra della figura.

Il circuito combinatorio C è integrato, e dunque risultano accessibili solo i 3 ingressi X1 X2 X3 e l'uscita Y. Supponendo nota la struttura interna dell'integrato, si vuole diagnosticare la presenza di un eventuale guasto del circuito semplicemente applicando una sequenza di segnali binari in ingresso e verificando che l'output Y corrisponda alla funzione booleana implementata.

Comunemente, il guasto di una porta logica viene modellato come uno "stack at one" (permanenza a 1), quando l'output della porta logica resta pari a 1 quale che siano i valori in ingresso, e "stack at zero" (permanenza a 0) quando invece la porta permane a zero per ogni valore degli ingressi.

Detta Y l'uscita dell'integrato, si identifichi una sequenza di n (n≤8) triple di input X1 X2 X3 (es: 000,010,011..) tale che un automa a stati finiti possa leggere sull'output Y la sequenza di bit prodotta dall'integrato, e diagnosticare l'eventuale presenza di un guasto. In particolare, l'automa deve produrre il seguente output a 3 bit:

000 = fase di valutazione ( ovvero: sequenza in esame), 001 = circuito funzionante correttamente

010 = AND oppure OR "stack at one", 011 = AND "stack at zero", 101 = OR "stack at zero"

Ovviamente, un guasto sulla porta OR non consente di diagnosticare un guasto contemporaneo sulla porta AND, ed un guasto di tipo "stack at one" sulla porta OR o sulla porta AND produce lo stesso effetto, dunque i due eventi non sono distinguibili dall'esterno (pertanto vengono segnalati con lo stesso output da parte dell'automa).

Si progetti l'automa per il test di C a un ingresso e tre uscite secondo il metodo formale visto a lezione.

<u>Suggerimento</u>: scrivete la funzione booleana (tabella di verità) di Y attesa per ciascuna possibile situazione (circuito funzionante, AND "stack at one", ecc.), ed identificate le triple X1X2X3 che consentono in modo non ambiguo di identificare una delle quattro possibili situazioni (funzionante, AND/OR stack at 1, ecc.). Ad esempio, la tripla 100 (x1x2x3) produce Y=1 solo se e solo se si è verificato un guasto AND/OR stack at 1.

Costruite poi l'automa che riceve in input esattamente la sequenza di queste triple.

Notate anche che non è necessario testare il circuito con tutte le possibili sequenze di ingresso (8).

Nota: Non è fondamentale ai fini della valutazione arrivare fino al progetto circuitale. E' invece fondamentale delineare la soluzione, motivandola, disegnare l'automa e la tabella degli stati futuri.

## **SOLUZIONI**

## Compito A

### Esercizio 1

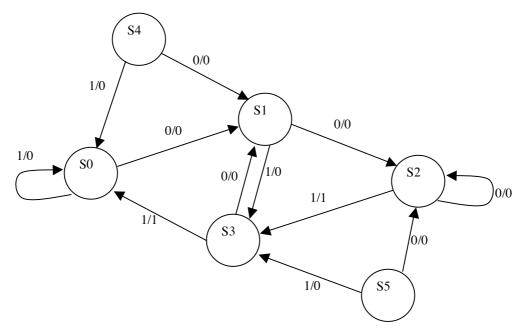

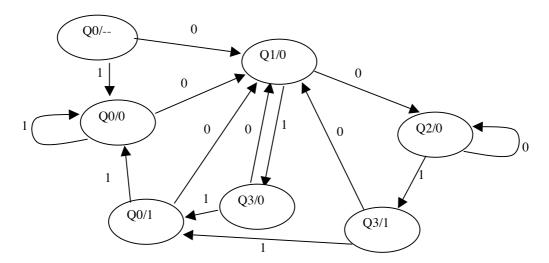

1) L'automa di Mealy in tabella è:

2) Per verificare se l'automa di Mealy è minimo costruiamo la tabella triangolare:

| S1         | (S1,S2)<br>(S0,S3) |                    |                    |    |                    |

|------------|--------------------|--------------------|--------------------|----|--------------------|

| S2         | X                  | X                  |                    |    |                    |

| <b>S</b> 3 | X                  | X                  | (S1,S2)<br>(S0,S3) |    |                    |

| S4         |                    | (S1,S2)<br>(S0,S3) | X                  | X  |                    |

| <b>S</b> 5 | (S1,S2)<br>(S0,S3) |                    | X                  | X  | (S1,S2)<br>(S0,S3) |

|            | S0                 | S1                 | S2                 | S3 | S4                 |

Una seconda analisi della tabella permette di vedere che tutte le caselle con le coppie si riferiscono a stati distinguibili, mentre sono indistinguibili gli stati S0 e S4 e gli stati S1 e S5.

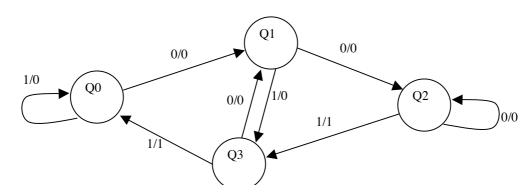

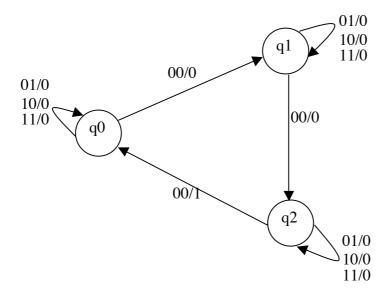

Quindi l'automa minimo è costituito dagli stati:  $Q0 = \{S0, S4\}, Q1 = \{S1, S5\}, Q2 = S2, Q3 = S3$  ed è rappresentato come segue:

- 3) L'automa di Moore equivalente ad un automa di Mealy si ottiene ponendo:

- uno stato iniziale indicato con Q0/-, che non produce output,

- per ognuno degli stati dell'automa di Mealy si distingue lo stato a cui si arriva producendo output 0 e lo stato a cui si arriva producendo 1,

- gli archi in modo consistente all'automa di Mealy.

L'automa di Moore equivalente all'automa minimo ricavato nel punto precedente:

4) Assegniamo ai quattro stati dell'automa di Mealy minimo la codifica Q0 = 00, Q1 = 01, Q2 = 10, Q3 = 11 ed indichiamo i due bit rispettivamente con b1 e b0. Il diagramma temporale ottenuto a fronte della sequenza di ingresso 01000110011 è il seguente:

### Esercizio 2

La tabella seguente fornisce i valori di f e g per tutti i possibili valori di x:

| <b>x3</b> | <b>x2</b> | x1 | <b>x0</b> | X  | f | g |

|-----------|-----------|----|-----------|----|---|---|

| 0         | 0         | 0  | 0         | 0  | 0 | 1 |

| 0         | 0         | 0  | 1         | 1  | 0 | 0 |

| 0         | 0         | 1  | 0         | 2  | 0 | 0 |

| 0         | 0         | 1  | 1         | 3  | 0 | 1 |

| 0         | 1         | 0  | 0         | 4  | 1 | 0 |

| 0         | 1         | 0  | 1         | 5  | 1 | 0 |

| 0         | 1         | 1  | 0         | 6  | 1 | 1 |

| 0         | 1         | 1  | 1         | 7  | 1 | 0 |

| 1         | 0         | 0  | 0         | -8 | 1 | 0 |

| 1         | 0         | 0  | 1         | -7 | 1 | 0 |

| 1         | 0         | 1  | 0         | -6 | 1 | 1 |

| 1         | 0         | 1  | 1         | -5 | 1 | 0 |

| 1         | 1         | 0  | 0         | -4 | 0 | 0 |

| 1         | 1         | 0  | 1         | -3 | 0 | 1 |

| 1         | 1         | 1  | 0         | -2 | 0 | 0 |

| 1         | 1         | 1  | 1         | -1 | 0 | 0 |

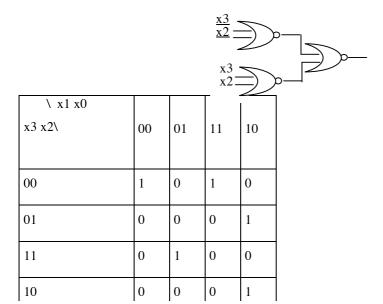

Dalle mappe di Karnaugh ricaviamo le espressioni minimali (i letterali complementati sono sottolineati):

| \ x1 x0<br>x3 x2\ | 00 | 01 | 11 | 10 |

|-------------------|----|----|----|----|

| 00                | 0  | 0  | 0  | 0  |

| 01                | 1  | 1  | 1  | 1  |

| 11                | 0  | 0  | 0  | 0  |

| 10                | 1  | 1  | 1  | 1  |

$$f = (\underline{x3} + \underline{x2})(x3 + x2)$$

A questa espressione, per le proprietà dell'algebra booleana, corrisponde il seguente circuito con sole porte NOR:

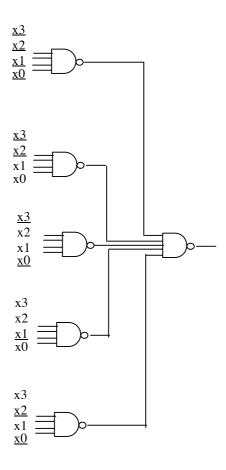

$$g = \underline{x3} \ \underline{x2} \ \underline{x1} \ \underline{x0} + \underline{x3} \ \underline{x2} \ \underline{x1} \ \underline{x0}$$

A questa espressione, per le proprietà dell'algebra booleana, corrisponde il seguente circuito con sole porte NAND:

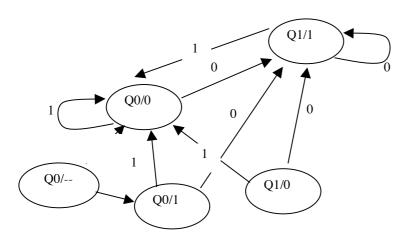

# Compito B

**Es 1**. Per la descrizione sintetica, si veda la soluzione del compito A. L'automa è il seguente

# Esercizio 2

L'automa è quello di un contatore mod 3 che cambia stato a fronte della coppia xy=00 e resta nello stato in cui si trova a fronte delle altre tre possibili coppie in ingresso.

Indichiamo i due bit di codifica degli stati w1 e w2 e utilizziamo la seguente codifica:

q0 = 00

q1=01

q2=10

La tavola di verità è la seguente :

| xyw1w2 | W1W2 | Z | j1k1       | j2k2 |

|--------|------|---|------------|------|

| 0000   | 01   | 0 | 0x         | x0   |

| 0001   | 10   | 0 | 1x         | 0x   |

| 0010   | 00   | 1 | <b>x</b> 1 | x0   |

| 0011   | XX   | X | XX         | XX   |

| 0100   | 00   | 0 | 0x         | x0   |

| 0101   | 01   | 0 | 0x         | 0x   |

| 0110   | 10   | 0 | x0         | x0   |

| 0111   | XX   | X | XX         | XX   |

| 1000   | 00   | 0 | 0x         | x0   |

| 1001   | 01   | 0 | 0x         | 0x   |

| 1010   | 10   | 0 | x0         | x0   |

| 1011   | XX   | X | XX         | XX   |

| 1100   | 00   | 0 | 0x         | x0   |

| 1101   | 01   | 0 | 0x         | 0x   |

| 1110   | 10   | 0 | x0         | x0   |

| 1111   | XX   | X | XX         | XX   |

Dalla tabella si ricava subito che:

$$j2 = k2 = 0$$

e minimizzando con Karnaugh si ottengono le espressioni:

$$j1 = \underline{x} \underline{y} w2$$

$$k1 = \underline{x} \underline{y}$$

$$z = \underline{x} \underline{y} w1$$

Lo schema circuitale si ottiene facilmente utilizzando le espressioni ricavate.

Le espressioni con FF di tipo D, ottenute minimizzando con le mappe di Karnaugh, sono:

$$d1 = \underline{x} \underline{y} w2 + y w1 + x w1$$

$$d2 = x y w1 w2 + y w2 + x w2$$

## Compito C

**Es.** 1

Per risolvere il problema, conviene (come suggerito) scrivere una tabella di verità che visualizzi, per ogni combinazione degli ingressi, l'output in assenza di errori, e quello che si otterrebbe in presenza dei vari errori. Nella tabella che segue sono riportati anche i valori in uscita alla porta AND.

| Input  | Output porta AND |         |         | Output porta OR (=Y) |           |                |           |

|--------|------------------|---------|---------|----------------------|-----------|----------------|-----------|

| x1x2x3 | ANDok A          | AND "1" | AND "0" | CircuitoOK           | ORoAND"1" | ORokAND"0'     | '   OR"0" |

| 1. 000 | 0                | 1       | 0       | 0                    | 1         | 0              | 0         |

| 2. 001 | 0                | 1       | 0       | 1                    | 1         | 1              | 0         |

| 3. 010 | 0                | 1       | 0       | 0                    | 1         | 0              | 0         |

| 4. 011 | 0                | 1       | 0       | 1                    | 1         | 1              | 0         |

| 5. 100 | 0                | 1       | 0       | 0                    | 1         | 0              | 0         |

| 6. 101 | 0                | 1       | 0       | 1                    | 1         | 1              | 0         |

| 7. 110 | 1                | 1       | 0       | 1                    | 1         | <mark>O</mark> | 0         |

| 8. 111 | 1                | 1       | 0       | 1                    | 1         | 1              | 0         |

Legenda:

ANDok = porta AND funzionante

AND"1" = porta AND stack-at-1 AND"1" = porta AND stack-at-0 CircuitoOK = circuito funzionante correttamente ORoAND"1" = la porta AND o la porta OR sono stack-at-1 ORokAND"0" = porta OR funziona correttamente, porta AND stack-at-0 OR"0" = porta OR stack-at-0

Osservate come alcune combinazioni di input consentano immediatamente di diagnosticare un errore. Ad esempio, l'input 5 produce output 0 solo in presenza di uno "stack at 1". Dunque, applicando questo input si può subito accertare ola presenza di questo errore. L'input 6 consente di diagnosticare invece l'errore OR "stack at 0", se l'output è zero. Infine, l'input 7 consente di diagnosticare l'errore AND "stack at 0".

Notate che basta applicare in sequenza gli input 5,6 e 7 per arrivare ad una diagnosi completa dei possibili eventi. L'automa è il seguente (ma si potrebbero trovare altre sequenze, ed altri ordini per la stessa sequenza):

Negli stati "grigi" il sistema permane, c X/010 cicli sono visualizzati solo per il primo stato mane).

rune to success output" per qualsiasi input (per semplicità i

Ricordiamo che gli output corrispondenti alle varie diagnosi sono:

000 = fase di valutazione ( ovvero: decisione in corso),001 = circuito funzionante correttamente

010 = AND oppure OR stack at one, 011 = AND stack at zero, 101 = OR stack at zero

Un errore commune nello svolgimento di questo esercizio è stato di non far transitare l'automa in uno stato finale una volta raggiunta una diagnosi certa.

In primo luogo, una volta diagnosticato un guasto, o uno stato di buon funzionamento, non ha senso lasciare che il sistema produca nuovi output. Ad esempio, la terna 100 consente di verificare la eventuale presenza di un guasto stackat-1. Se questo guasto viene individuato, quali che siano i successive valori di y, l'output dell'automa DEVE RESTARE 010, NON Può CAMBIARE, I guasti sono permanenti!

E' facile intuire inoltre che, in un sistema reale, l'output dell'automa debba segnalare all'esterno la presenza di un malfunzionamento nel circuito integrato, e perciò il segnale di errore deve essere permanente, almeno fino a che il circuito difettoso viene rimosso e rimpiazzato da un altro circuito da testare (ovviamente, identico, visto che l'automa è tarato per testare un certo tipo di circuito digitale, utilizzando una ben precisa sequenza di test).

#### Per maggiore chiarezza:

Il test di correttezza consiste nell'applicare una sequenza di input al circuito da testare e collegare l'output ad un circuito sequenziale (rappresentato da un automa) che ne "interpreta" il significato.

Nello svolgimento è stata scelta una certa sequenza, ma altre scelte erano possibili.

Si applica dapprima la "terna" 100 al circuito integrato. L'automa ne legge l'output: se l'output è 1, come da tabella di verità, siamo in presenza di un errore <u>OR or AND stack-at-1</u>. Se invece l'output è zero, non si può decidere, e bisogna rimandare la decisione all'esame del successivo valore prodotto dal circuito.

Si applica successivamente la terna "101". Se l'output è 0, siamo in presenza di un errore <u>OR stack-at-0</u>, altrimenti, bisogna rimandare la decisione all'esame del successivo valore prodotto dal circuito.

Infine, si applica la terna "110". Se l'output è 1, il circuito <u>funziona correttamente</u>, altrimenti, siamo in presenza di un errore <u>AND stack-at-0</u>.

L'automa ha 7 stati, dunque occorrono 3 FF. Per semplicità, si possono usare FF D.

L'automa si può facilmente sintetizzare con il procedimento visto a lezione.