## SECONDO ESONERO di PROGETTAZIONE di SISTEMI DIGITALI a.a. 2014/15 proff. Gorla e Massini

FILA A

| Nome e Cognome             |                                 |                 |

|----------------------------|---------------------------------|-----------------|

| ☐ Canale A-L (prof. Gorla) | ☐ Canale M-Z (prof.ssa Massini) | ☐ Teledidattica |

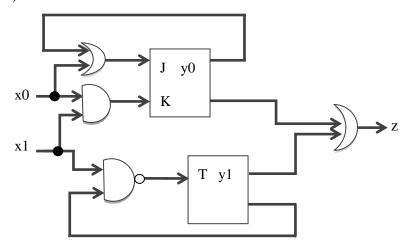

Esercizio 1 (7 punti). Si analizzi il seguente circuito sequenziale, arrivando fino al disegno dell'automa (non necessariamente minimo):

Esercizio 2 (5 punti). Si minimizzi il seguente automa di Mealy con stato iniziale S0 (3 punti) e si trasformi l'automa risultante nell'automa di Moore equivalente (2 punti).

|            | 0    | 1    |

|------------|------|------|

| S0         | S0/0 | S3/1 |

| <b>S</b> 1 | S1/0 | S2/0 |

| S2         | S5/0 | S1/1 |

| <b>S</b> 3 | S3/0 | S4/0 |

| S4         | S5/0 | S3/1 |

| S5         | S4/0 | S1/1 |

Esercizio 3 (5 punti). Si disegni un contatore di impulsi di clock alla rovescia modulo 16, senza mostrare la procedura di sintesi (2 punti) (SOLO PER IL CANALE A-L: lo studente è libero di realizzarlo come contatore sincrono o asincrono). Si mostri poi il suo funzionamento disegnando il diagramma temporale per 8 colpi di clock partendo dallo stato 0010 (3 punti).

Esercizio 4 (8 punti). Si realizzi un circuito sequenziale che prenda in input una sequenza di bit e che dia in output 1 se negli ultimi 3 bit ci sono almeno due 1.

ESEMPIO: IN: 01101010010111...

OUT: 00111010000111...

Per la sintesi, si utilizzi un FF di tipo SR per il bit più significativo e FF di tipo D per tutti gli altri bit; si usi inoltre una ROM per la realizzazione della parte combinatoria.

Esercizio 5 (7 punti). Si progetti una interconnessione tra 4 registri R0, R1, R2 ed R3 tale che:

- R0 viene trasferito in R1 quando il bit più significativo di R0 è diverso dal suo bit meno significativo;

- R1 viene trasferito in R2, se R2 è pari, o in R3, altrimenti;

- R0 riceve il contenuto di R2, se la somma di R2 ed R3 non dà luogo a overflow, o il contenuto di R3, altrimenti.

Tutti i trasferimenti sono controllati da un segnale globale in\_R, che abilita i trasferimenti quando vale 1. Si rappresenti l'interconnessione richiesta facendo uso di moduli combinatori noti (ADD, CMP, MUX, DEC, ...).

## SECONDO ESONERO di PROGETTAZIONE di SISTEMI DIGITALI a.a. 2014/15 proff. Gorla e Massini

FILA B

| Nome e Cognome             |                                 |                 |

|----------------------------|---------------------------------|-----------------|

| ☐ Canale A-L (prof. Gorla) | ☐ Canale M-Z (prof.ssa Massini) | ☐ Teledidattica |

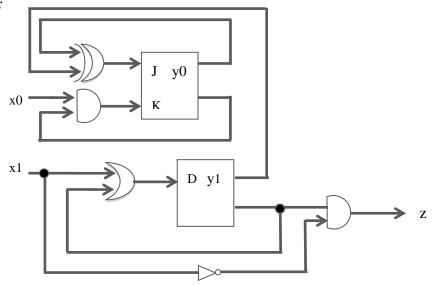

Esercizio 1 (7 punti). Si analizzi il seguente circuito sequenziale, arrivando fino al disegno dell'automa (non

necessariamente minimo):

Esercizio 2 (5 punti). Si minimizzi il seguente automa di Mealy con stato iniziale F (3 punti) e si trasformi l'automa risultante nell'automa di Moore equivalente (2 punti).

|   | 0   | 1   |

|---|-----|-----|

| A | A/0 | C/0 |

| В | B/0 | E/0 |

| С | D/0 | B/1 |

| D | C/0 | A/1 |

| Е | E/0 | A/1 |

| F | F/1 | C/1 |

Esercizio 3 (5 punti). Si disegni un contatore di impulsi di clock bidirezionale modulo 8, senza mostrare la procedura di sintesi (2 punti) (SOLO PER IL CANALE A-L: lo studente è libero di realizzarlo come contatore sincrono o asincrono). Si mostri poi il suo funzionamento disegnando il diagramma temporale per 8 colpi di clock, partendo dallo stato 010 e assumendo che per i primi tre colpi di clock conti alla rovescia e poi cominci a contare in avanti (3 punti).

Esercizio 4 (8 punti). Si realizzi un circuito sequenziale che prende in input una sequenza di bit e dà in output 1 se gli ultimi tre bit ricevuti rappresentano un multiplo di 3.

ESEMPIO: IN: 01100011010111...

*OUT*: 00110101100010...

Per la sintesi, si utilizzi un FF di tipo JK per il bit più significativo e FF di tipo D per tutti gli altri bit; si usi una ROM per la realizzazione della parte combinatoria.

Esercizio 5 (7 punti). Si progetti una interconnessione tra 4 registri R0, R1, R2 ed R3 tale che:

- R0 viene trasferito in R1, se la somma di R1 ed R2 è negativa, in R2, altrimenti;

- R3 viene trasferito in R0 se R0 è un multiplo di 4;

- R3 riceve il contenuto di R1, se la somma di R1 ed R2 è maggiore di R0, altrimenti riceve R2.

Tutti i trasferimenti sono controllati da un segnale globale in\_R, che abilita i trasferimenti quando vale 1. Si rappresenti l'interconnessione richiesta facendo uso di moduli combinatori noti (ADD, CMP, MUX, DEC, ...).