## ESAME di PROGETTAZIONE di SISTEMI DIGITALI

15 Luglio 2014 – proff. Gorla e Massini

Nome e Cognome \_\_\_\_\_

Esercizio 1 (2 punti) Dato  $X = -29,675_{10}$ , lo si converta in base 2 nella rappresentazione in virgola mobile, usando 10 bit per la mantissa e 4 per l'esponente.

**Esercizio 2 (4 punti)** Dati  $A = -24_{10}$  e  $B = 37_{10}$  li si converta nella rappresentazione in complemento a 2 e si esegua la somma A+B e la differenza A-B in tale rappresentazione, verificando i due risultati. **N.B.** Per rappresentare A e B usare il numero di bit necessario per esprimere sia A+B che A-B.

**Esercizio 3 (3 punti)** Disegnare l'automa che riceve in ingresso un bit x e produce in uscita 1 se negli ultimi 3 bit ricevuti c'è un solo 1, anche nel caso di eventuali sovrapposizioni.

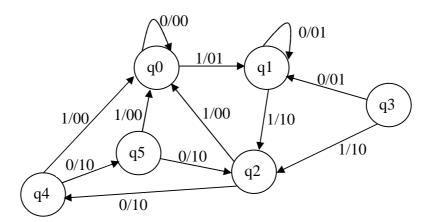

**Esercizio 4 (8 punti)** Dato il seguente automa, eseguire la procedura di minimizzazione (2 punti) e disegnare l'automa minimo (1 punto).

Progettare la rete sequenziale che realizza l'automa minimo. In particolare: stendere la tavola degli stati futuri considerando un flip flop di tipo D per il bit più significativo e un flip flop di tipo JK per il secondo (2 punti); ricavare le espressioni minimali per le funzioni di eccitazione e le uscite (2 punti); disegnare il circuito (1 punto).

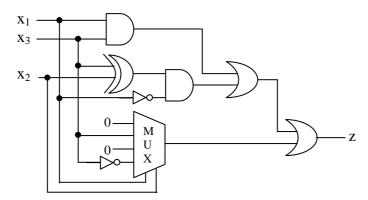

## Esercizio 5 (8 punti) Dato il circuito in figura:

- a) Si ricavi l'espressione di z (2 punti).

- b) Si ricavi dall'espressione ottenuta nel punto a), l'espressione in forma canonica SOP (1 punto).

- c) Si scriva l'espressione in forma minimale POS (1 punto).

- d) Si realizzi z con PLA (2 punti).

- e) Si realizzi z con sole porte NAND (2 punti).

**Esercizio 6 (6 punti).** Si considerino 4 registri sorgente  $S_1$ ,  $S_2$ ,  $S_3$  e  $S_4$  e un registro destinazione D. Si progetti la rete di interconnessione che permette i seguenti trasferimenti:

- se  $S_3$  è pari e non negativo  $\rightarrow$  il prodotto logico ( $S_1$  AND  $S_2$ ) viene trasferito in D;

- se S<sub>3</sub> è pari e negativo → S<sub>2</sub> viene trasferito in D;

- se  $S_3$  è dispari e non negativo  $\rightarrow$   $S_3$  viene trasferito in D;

- se  $S_3$  è dispari e negativo  $\rightarrow$  la somma algebrica  $(S_3 + S_4)$  viene trasferita in D.

Il trasferimento in D è abilitato se  $S_1 > S_2$ .

Si specifichi lo schema di interconnessione con tutti i segnali di controllo, usando moduli combinatori noti (per es., ADD, MUX, DECOD, ...) con ingressi e uscite da *n* bit.