Si progetti un sistema di trasferimento fra i registri R<sub>0</sub>, R<sub>1</sub> ed R<sub>2</sub> tale che:

- $R_0$  viene portato in  $R_1$  se  $R_1 > R_2$ ;

- $R_1$  viene portato in  $R_2$  se  $R_0 < R_1$ ;

- $R_2$  viene portato in  $R_0$  se  $R_0=R_1\mid R_2$  (dove  $\mid$  indica l'OR bit a bit). Si utilizzino nel progetto moduli combinatori noti (per esempio, ADD, CMP, ...)

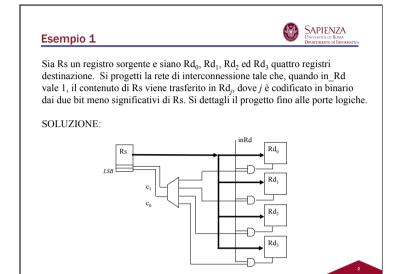

## SOLUZIONE:

La rete di interconnessione si realizza mettendo insieme tre schemi di trasferimento 1-a-1:

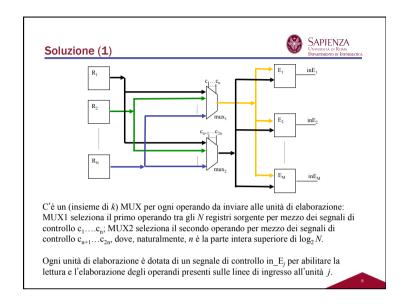

## Soluzione (1) Bisogna poi progettate la parte circuitale che permette di ottenere i valori dei segnali di controllo in $R_0$ , in $R_1$ e in $R_2$ . Le condizioni poste per ottenere i primi due trasferimenti suggeriscono di utilizzare le uscite di due comparatori:

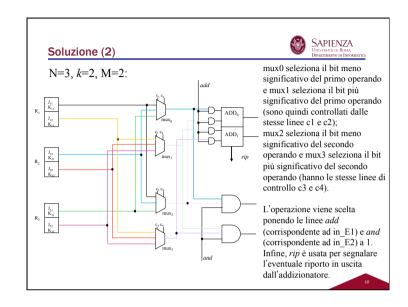

## Soluzione (2)

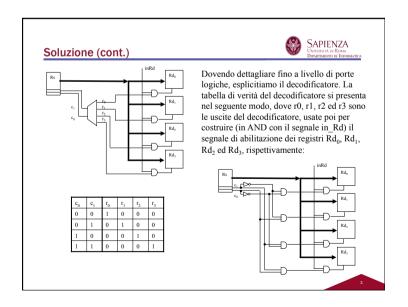

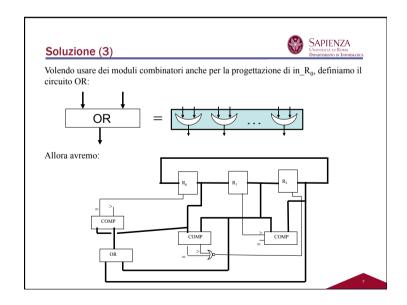

Per progettare la parte combinatoria che permette di ottenere in\_ $R_0$  seguiamo il metodo di sintesi visto per le reti combinatorie. Siano  $x_1, \dots x_k, y_1, \dots y_k$  e  $z_1, \dots z_k$  i bit contenuti in  $R_0$ ,  $R_1$  ed  $R_2$  rispettivamente. Ovviamente, l'uguaglianza at a  $R_0$  e l'OR bit a bit tra  $R_1$  ed  $R_2$  si ottiene verificando l'uguaglianza bit a bit; pertanto, stendiamo la tabella di verità che ci permette di trovare la funzione  $c_1$  tale che  $c_1$  = 1 se e solo se  $x_1$  =  $y_1$  OR  $z_1$ :

| $\mathbf{x}_{i}$ | $\mathbf{y}_{i}$ | $\mathbf{z}_{\mathrm{i}}$ | c <sub>i</sub> |

|------------------|------------------|---------------------------|----------------|

| 0                | 0                | 0                         | 1              |

| 0                | 0                | 1                         | 0              |

| 0                | 1                | 0                         | 0              |

| 0                | 1                | 1                         | 0              |

| 1                | 0                | 0                         | 0              |

| 1                | 0                | 1                         | 1              |

| 1                | 1                | 0                         | 1              |

| 1                | 1                | 1                         | 1              |

|                  |                  |                           |                |

Dalla mappa di Karnaugh si ottiene la seguente espressione per  $c_i$ :

$$c_i = \overline{x}_i \overline{y}_i \overline{z}_i + x_i (y_i + z_i)$$

Mettendo in AND tutte le condizioni  $c_i$  ottenute con il metodo appena illustrato, si ottiene la condizione in  $R_0$ .

## Esempio 3

Progettare una rete di interconnessione "molti-molti" che consenta di caricare il contenuto di 2 fra N registri  $R_1...R_N$  da k bit su 1 fra M dispositivi di elaborazione  $E_1....E_M$  a due ingressi (la comunicazione avviene fra 2 su N sorgenti ed 1 su M destinazioni).

Disegnare lo schema a blocchi evidenziando tutti i segnali di controllo necessari per:

- selezionare 2 fra gli N registri sorgente (ovvero i due operandi);

- convogliare i 2 operandi in ingresso ad uno fra gli *M* dispositivi di elaborazione

Disegnare poi lo schema circuitale (quindi con tutti i dettagli fino al livello di FF, porte logiche, numero e ruolo dei segnali di controllo necessari) per il caso di:

- 3 registri sorgente a due bit (N=3, k=2), con FF di tipo JK;

- 2 dispositivi destinazione (M=2), di cui uno sia un sommatore aritmetico e l'altro un circuito logico che esegua l'AND bit a bit fra i due registri sorgente selezionati.