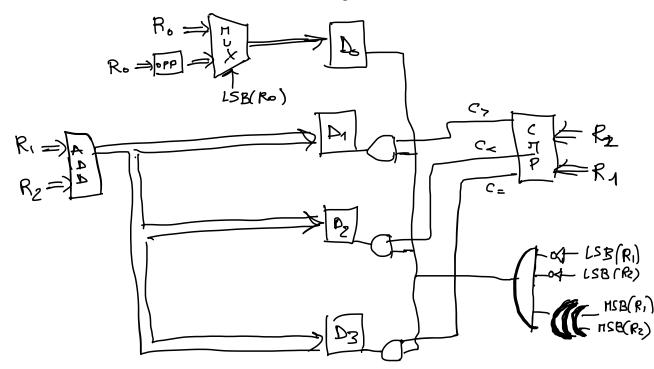

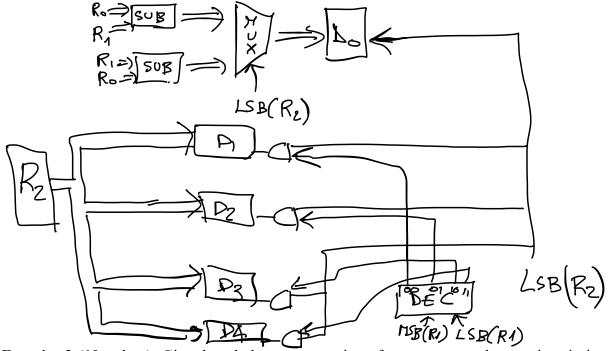

Exercise 1 (4 points): Consider the source registers R0, R1 and R2, and the destination registers D0, D1, D2 and D3. Design an interconnection schema such that:

- in D0 is moved R0, if R0 itself is even, otherwise it is moved the opposite of R0;

- the sum between R1 and R2 is moved in D1 if R2> R1, in D2 if R2<R1, in D3 if R1=R2.

Transfers are enabled if R1 and R2 are even and with different sign.

Exercise 2 (3 points): By using axioms and laws of Boolean algebra, prove the following identity:

$$\frac{(a\overline{b} + \overline{b}c + c(\overline{a} + b))\oplus ac}{(a\overline{b} + (b + \overline{c}))(\overline{c} + a\overline{b})} \oplus ac$$

$$= (a\overline{b} + b\overline{c} + \overline{c} + a\overline{b}\overline{c}) \oplus ac$$

$$= (a\overline{b} + \overline{c}) \oplus ac$$

$$= (a\overline{b} + \overline{c})(\overline{ac}) + (\overline{a}\overline{b} + \overline{c}) \oplus c$$

$$= (a\overline{b} + \overline{c})(\overline{ac}) + (\overline{a}\overline{b} + \overline{c}) \oplus c$$

$$= (a\overline{b} + \overline{c})(\overline{a} + \overline{c}) + (\overline{a} + b)ac$$

$$= a\overline{b}\overline{c} + a\overline{c} + \overline{c} + abc$$

$$= \overline{c} + abc = (\overline{c} + ab)(\overline{c} + c) = ab + \overline{c}$$

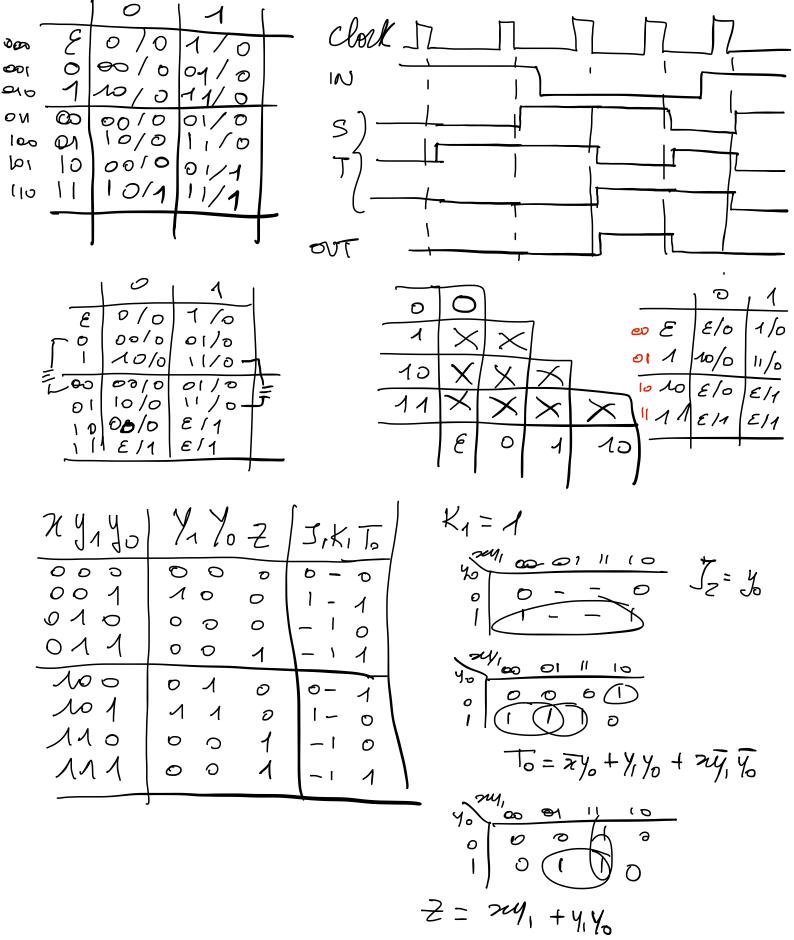

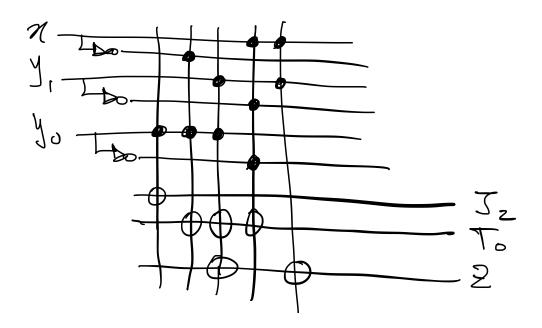

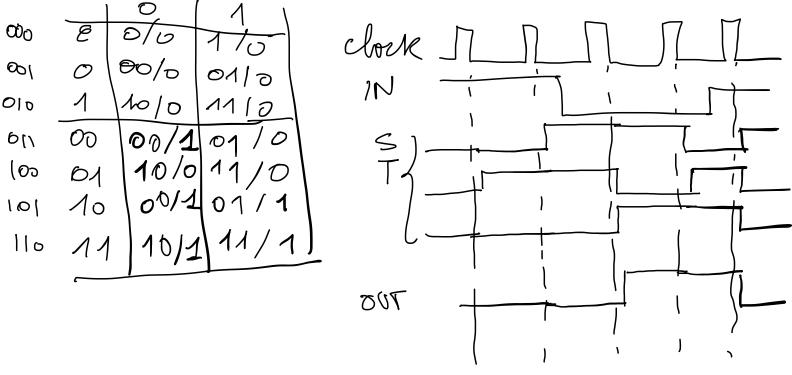

**Exercise 3 (10 points)**: Give the tabular representation of an automaton that receives in input a bit sequence and gives in output 1 whenever the last 3 bits, seen as an integer 2-complement, represent a negative number that is not multiple of 4, by also considering overlappings; when 3 bits have not been received yet, return 0. Then, draw the temporal diagram with input 11001. Finally, modify the automaton not to admit overlappings and synthetize the associated circuit, by using a JK FF for the most signifying bit, T FFs for the remaining bits, and a PLA for the combinatorial part.

**Exercise 4 (5 points)**: Consider the hexadecimal number 2A5B and subtract to it in base 16 the hexadecimal number 9C7. Then, convert the result in a binary sequence of 16 bits, to be considered as a rational number in IEEE 754 half-precision format. Subtract from this number the rational number <1;01001;110000000>, still expressed in IEEE half-precision format, and write the result in the same format.

$$2A5B - 1,110000000000 + 0,100100 + 0,100100 + 0,100100 + 0,100 = 0,100100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,100 + 0,1000 + 0,1000 + 0,100 + 0,1000 + 0,1000 + 0,100 + 0,100 + 0,1000 + 0,1$$

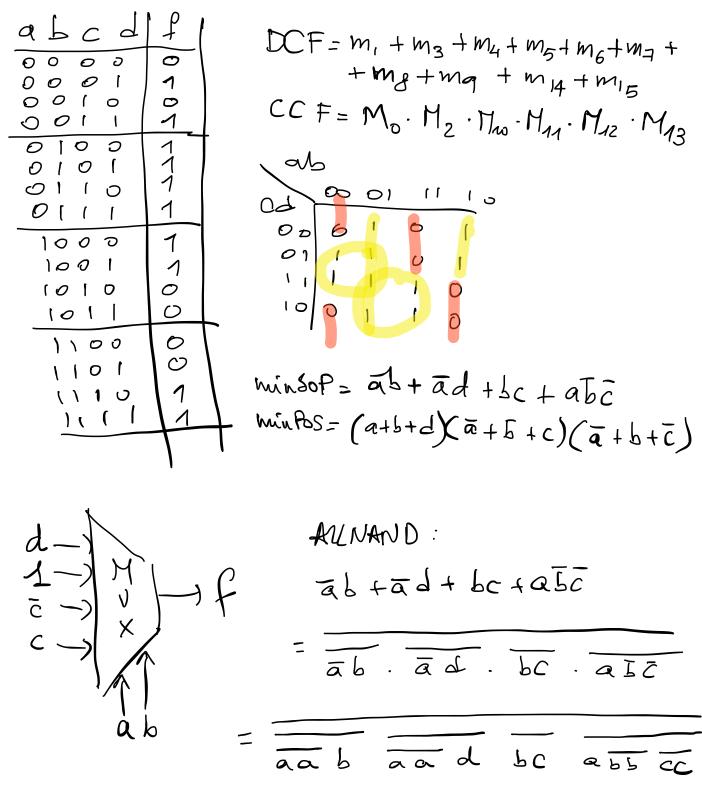

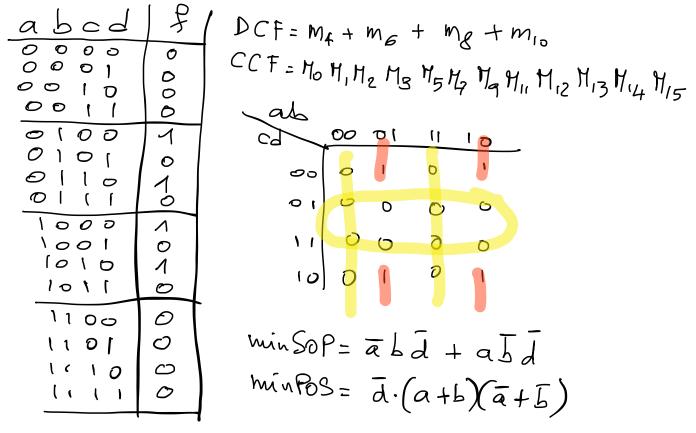

**Exercise 5 (1+1+2+2+2 points):** The 4 variables function f(a,b,c,d) holds 0 if  $a(b \oplus c)=1$  or if a+b+d=0.

- Provide the truth table for f

- Write the canonical SOP and POS expressions for f

- Write the minimal SOP and POS expressions for *f*

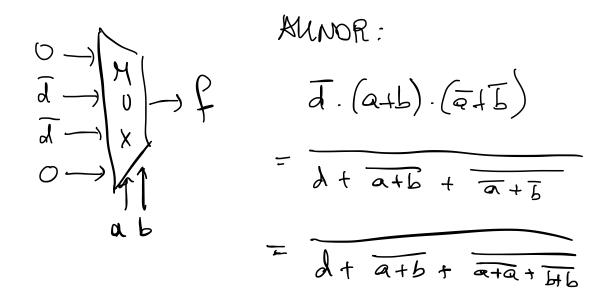

- Realize *f* by using a MUX with 4 inputs

- Write *f* in ALL-NAND form

Name:

**Exercise 1 (1+1+2+2+2 points):** The 4 variables function f(a,b,c,d) holds 0 if  $(\bar{a} + b)(a + \bar{b})=1$  or if  $a \oplus b \oplus d=0$ .

- Provide the truth table for f

- Write the canonical SOP and POS expressions for f

- Write the minimal SOP and POS expressions for f

- Realize *f* by using a MUX with 4 inputs

- Write f in ALL-NOR form

aRJ

**Exercise 2 (4 points)**: Consider the source registers R0, R1 and R2, and the destination registers D0, D1, D2, D3 and D4. Design an interconnection schema such that:

- in D0 is moved R0-R1, if R2 is even, otherwise it is moved R1-R0;

- R2 is moved in D1, if R1 is even and non-negative, in D2, if R1 is odd and non-negative, in D3, if R1 is even and negative, in D4, if R1 is odd and negative.

Transfers are enabled if R0 is not multiple of 2.

**Exercise 3 (10 points)**: Give the tabular representation of an automaton that receives in input a bit sequence and gives in output 1 whenever the last 3 bits, seen as an integer 2-complement, represent a number that is either negative or multiple of 4, by also considering overlappings; when 3 bits have not been received yet, return 0. Then, draw the temporal diagram with input 11001. Finally, modify the automaton not to admit overlappings and synthetize the associated circuit, by using a JK FF for the most signifying bit, T FFs for the remaining bits, and a PLA for the combinatorial part.

$\mathcal{O}$ 0/0  $\overline{\mathcal{E}}$ 1/0 ര്മാ 01/0 00/0 Ð 1 00 11/0 10/0 1 010 01/0  $\mathcal{E}/1$ 110 DO 11/0 E/1 01 10/6 E/1 100 10 101 110 11 E [1  $\varepsilon / 1$

10

Ø 0 Ο ଚ

10

0

+ = y1% + = y2 y1

0 - -

= yy , + zy

00

ſ

D

⇒Jz **≯** ۲⁄2

<u>→<u>T</u></u>

2

อ

Y1, Y0

**Exercise 4 (3 points):** By using axioms and laws of Boolean algebra, prove the following identity:  $(x\overline{z} + \overline{yz} + y(x + \overline{z})) \oplus xy = \overline{y} + xz$

$$\begin{aligned} \left[ \begin{array}{c} x \overline{z} + (\overline{y} + \overline{z}) \cdot (\overline{y} + \overline{z} \overline{z}) \right] & \oplus xy \\ &= \left( \chi \overline{z} + \overline{y} + \overline{x} \overline{y} \overline{z} + \overline{y} \overline{z} \right) & \oplus xy \\ &= \left( \chi \overline{z} + \overline{y} \right) & \oplus xy \\ &= (\chi \overline{z} + \overline{y}) & \oplus \chi \overline{y} \\ &= (\chi \overline{z} + \overline{y}) (\overline{x} + \overline{y}) + (\overline{x} + \overline{z}) xy \\ &= \chi \widehat{y} \overline{z} + \overline{x} \overline{y} + \overline{y} + \overline{y} \overline{y} z \\ &= \overline{y} + \chi \overline{y} \overline{z} \\ &= (\overline{y} + \chi \overline{z}) (\overline{y} + \overline{y}) = \chi \overline{z} + \overline{y} \end{aligned}$$

**Exercise 5 (5 points)**: Consider the hexadecimal number 4A5B and subtract to it in base 16 the hexadecimal number 6C1. Then, convert the result in a binary sequence of 16 bits, to be considered as a rational number in IEEE 754 half-precision format. Subtract from this number the rational number <1;10001;111000000>, still expressed in IEEE half-precision format, and write the result in the same format.