# Exercises on the topics of class 14

## **Exercises with solutions**

**Ex. 1.** A 4 variables BF  $f(x_4, x_3, x_2, x_1)$  holds 1 if  $x_4 + x_2 x_1 = 0$ , whereas it is not specified (don't care terms) if  $x_4 x_1 = 1$ . Design a circuit that implements f through a PLA and a MUX.

### **SOLUTION:**

The TT of the function is:

| x4 | <b>x</b> 3 | <b>x2</b> | <b>x1</b> | f |

|----|------------|-----------|-----------|---|

| 0  | 0          | 0         | 0         | 1 |

| 0  | 0          | 0         | 1         | 1 |

| 0  | 0          | 1         | 0         | 1 |

| 0  | 0          | 1         | 1         | 0 |

| 0  | 1          | 0         | 0         | 1 |

| 0  | 1          | 0         | 1         | 1 |

| 0  | 1          | 1         | 0         | 1 |

| 0  | 1          | 1         | 1         | 0 |

| 1  | 0          | 0         | 0         | 0 |

| 1  | 0          | 0         | 1         | - |

| 1  | 0          | 1         | 0         | 0 |

| 1  | 0          | 1         | 1         | - |

| 1  | 1          | 0         | 0         | 0 |

| 1  | 1          | 0         | 1         | - |

| 1  | 1          | 1         | 0         | 0 |

| 1  | 1          | 1         | 1         | - |

The KM is:

| \ x2 x1<br>x4 x3 \ | 00 | 01 | 11 | 10 |

|--------------------|----|----|----|----|

| 00                 | 1  | 1  | 0  | 1  |

| 01                 | 1  | 1  | 0  | 1  |

| 11                 | 0  | х  | x  | 0  |

| 10                 | 0  | х  | x  | 0  |

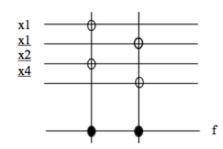

and so, the resulting minimal SOP for f is  $\underline{x_2} x_1 + \underline{x_4} \underline{x_1}$  From this, we can obtain the PLA:

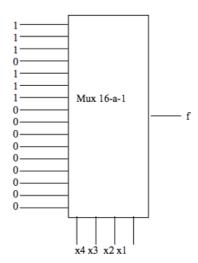

For the realization with a MUX, we can choose a 16-to-1. For the don't care symbols, we can indifferently choose to put a 0 or a 1 in that entrance (in this solution, we choose 0 for all don't cares):

**Ex. 2.** Design a combinatorial circuit that computes function y = x + 3, where x is a 4-bits 2 complement integer in [-8, 7] and y is codified in the same format. Put "don't care" symbols whenever y cannot be represented in the given format.

Use a PLA for the two less signifying bits of y, a ROM for all the function and a MUX 8-to-1 for the second most signifying bit.

#### SOLUTION:

The required function is:

| $X_3$ | $X_2$ | $X_1$ | $X_{\theta}$ | $Y_3$ | $Y_2$ | $Y_1$ | $Y_{\theta}$ |

|-------|-------|-------|--------------|-------|-------|-------|--------------|

| 0     | 0     | 0     | 0            | 0     | 0     | 1     | 1            |

| 0     | 0     | 0     | 1            | 0     | 1     | 0     | 0            |

| 0     | 0     | 1     | 0            | 0     | 1     | 0     | 1            |

| 0     | 0     | 1     | 1            | 0     | 1     | 1     | 0            |

| 0     | 1     | 0     | 0            | 0     | 1     | 1     | 1            |

| 0     | 1     | 0     | 1            | _     | -     | -     | -            |

| 0     | 1     | 1     | 0            | -     | -     | -     | -            |

| 0     | 1     | 1     | 1            | -     | -     | -     | -            |

| 1     | 0     | 0     | 0            | 1     | 0     | 1     | 1            |

| 1     | 0     | 0     | 1            | 1     | 1     | 0     | 0            |

| 1     | 0     | 1     | 0            | 1     | 1     | 0     | 1            |

| 1     | 0     | 1     | 1            | 1     | 1     | 1     | 0            |

| 1     | 1     | 0     | 0            | 1     | 1     | 1     | 1            |

| 1     | 1     | 0     | 1            | 0     | 0     | 0     | 0            |

| 1     | 1     | 1     | 0            | 0     | 0     | 0     | 1            |

| 1     | 1     | 1     | 1            | 0     | 0     | 1     | 0            |

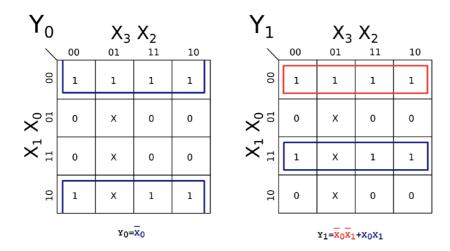

We can now compute the minimal SOP for the two less signifying bits:

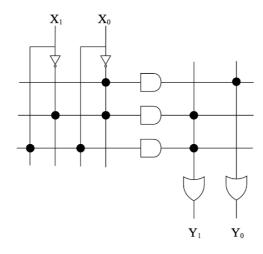

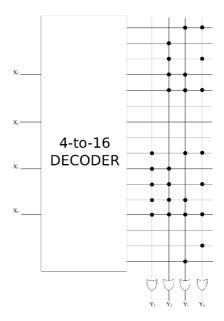

and so the PLA is:

The ROM is codified by looking at the TT of the function:

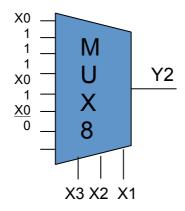

For the MUX, we use as control lines  $X_3$ ,  $X_2$  and  $X_1$ . Don't care symbols can be freely put to 0 or 1, but in our case it turns out that all 1s is a good option. So, the resulting circuit is:

### **Exercises without solutions**

**Ex. 1.** Design a PLA for the 4-variables function f(x3, x2, x1, x0) = m2 + m3 + m4 + m9 that is not defined (don't care) in m0, m1, m6 and m11.

**Ex. 2.** Design two 4-to-1 MUXs for the two 3-variables BFs f(a2, a1, a0) = m0+m3+m6+m7 and g(a2, a1, a0) = m2+m4+m5+m6.

**Ex. 3.** Consider the following BF:

| х | у | Z | tΙ | t2 | t3 | <i>t4</i> |

|---|---|---|----|----|----|-----------|

| 0 | 0 | 0 | 0  | 0  | 0  | 0         |

| 0 | 0 | 1 | 0  | 1  | 1  | 0         |

| 0 | 1 | 0 | 1  | 0  | 0  | 1         |

| 0 | 1 | 1 | 1  | 1  | 1  | 0         |

| 1 | 0 | 0 | 1  | 0  | 0  | 1         |

| 1 | 0 | 1 | 1  | 1  | 0  | 0         |

| 1 | 1 | 0 | 1  | 1  | 0  | 1         |

| 1 | 1 | 1 | 0  | 0  | 0  | 1         |

- a) Design a ROM for this BF.

- b) Compute t1 and t4 through a PLA.

- c) Compute t2 and t3 through a 4-to-1 MUX and a 2-to-1 MUX, respectively.