# Communication-Avoiding Parallel Recursive Algorithms for Matrix Multiplication

Benjamin Lipshitz

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2013-100 http://www.eecs.berkeley.edu/Pubs/TechRpts/2013/EECS-2013-100.html

May 17, 2013

Copyright © 2013, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Communication-Avoiding Parallel Recursive Algorithms for Matrix Multiplication

by

Benjamin Lipshitz

A thesis submitted in partial satisfaction of the requirements for the degree of

Master of Science

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor James Demmel, Chair Professor Katherine Yelick Professor Armando Fox

Spring 2013

## $\begin{array}{c} {\bf Communication\hbox{-}Avoiding\ Parallel\ Recursive\ Algorithms\ for\ Matrix}\\ {\bf Multiplication} \end{array}$

$\begin{array}{c} \text{Copyright 2013} \\ \text{by} \\ \text{Benjamin Lipshitz} \end{array}$

## Contents

| Co | ontents                                                                                                                                                                                                                                                                                                                                               | i                                                    |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Li | ist of Figures                                                                                                                                                                                                                                                                                                                                        | iii                                                  |

| Li | ist of Tables                                                                                                                                                                                                                                                                                                                                         | iv                                                   |

| 1  | Introduction1.1 Communication Model1.2 Iterative Parallel Matrix Multiplication Algorithms1.3 Parallelizing Recursive Algorithms1.4 The Loomis-Whitney Inequality                                                                                                                                                                                     | 1<br>2<br>3<br>3<br>4                                |

| 2  | Strassen's Matrix Multiplication  2.1 Strassen-Winograd Algorithm  2.2 Communication Lower Bounds  2.3 Communication-Avoiding Parallel Strassen  2.4 Analysis of Other Algorithms  2.5 Performance Results  2.6 Performance Model  2.7 Implementation Details  2.8 Numerical Stability  2.9 Parallelizing Other Fast Matrix Multiplication Algorithms | 5<br>6<br>6<br>7<br>15<br>20<br>25<br>31<br>35<br>36 |

| 3  | Classical Rectangular Matrix Multiplication3.1 Communication Lower Bounds3.2 CARMA Algorithm3.3 Performance Results3.4 Remarks                                                                                                                                                                                                                        | 38<br>40<br>44<br>48<br>51                           |

| 4  | Sparse Matrix Multiplication4.1 Preliminaries                                                                                                                                                                                                                                                                                                         | <b>54</b> 55 56 59                                   |

| •   | • |

|-----|---|

| 1   | 1 |

| - 1 | 1 |

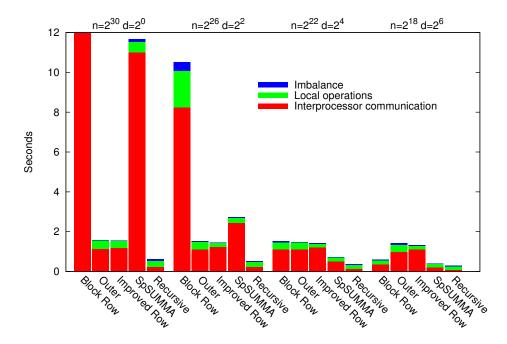

|              | 4.4 Performance Results                            | 63         |

|--------------|----------------------------------------------------|------------|

| 5            | Beyond Matrix Multiplication                       | 68         |

|              | 5.1 Naïve <i>n</i> -body Interaction               | 68         |

|              | 5.2 Dealing with Dependencies                      | 70         |

|              | 5.3 All-Pairs Shortest Paths                       | 70         |

|              | 5.4 Triangular Solve with Multiple Righthand Sides | 71         |

|              | 5.5 Cholesky Decomposition                         | 73         |

| 6            | Discussion and Open Questions                      | <b>7</b> 5 |

| Bibliography |                                                    |            |

## List of Figures

| 1.1  | The computation rectangular prism for matrix multiplication                                                                                                                                                                                    | 4               |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.1  | Representation of BFS and DFS steps                                                                                                                                                                                                            | 8               |

| 2.2  | An example matrix layout for CAPS                                                                                                                                                                                                              | 10              |

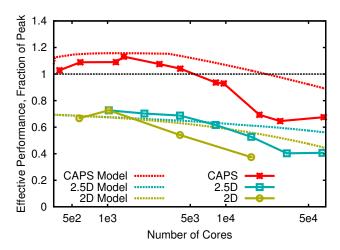

| 2.3  | Bandwidth costs and strong scaling of matrix multiplication: classical vs. Strassenbased. Horizontal lines correspond to perfect strong scaling. $P_{min}$ is the minimum number of processors required to store the input and output matrices | 18              |

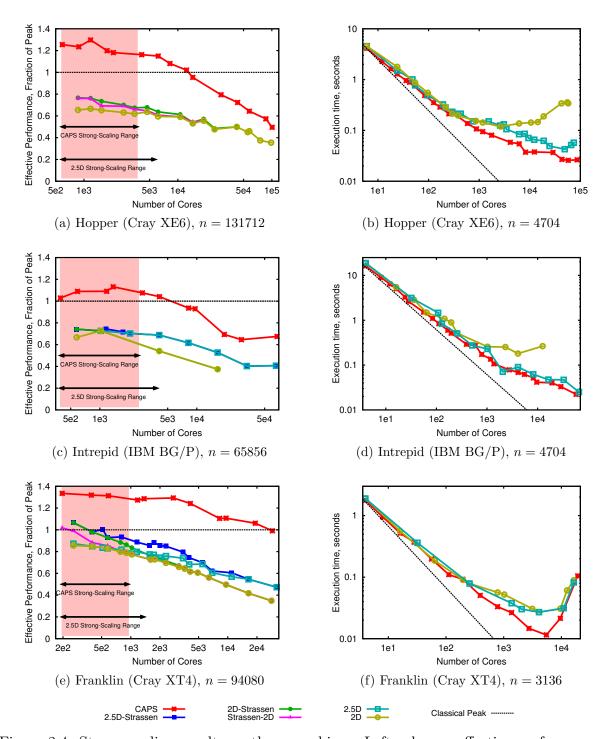

| 2.4  | Strong scaling results for CAPS                                                                                                                                                                                                                | $\frac{10}{22}$ |

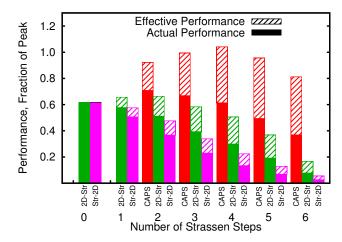

| 2.4  | Efficiency at various numbers of Strassen steps                                                                                                                                                                                                | $\frac{22}{25}$ |

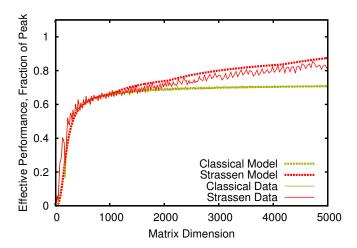

| 2.6  | Comparison of the sequential model to the actual performance of classical and                                                                                                                                                                  | 20              |

| 2.0  | Strassen matrix multiplication                                                                                                                                                                                                                 | 26              |

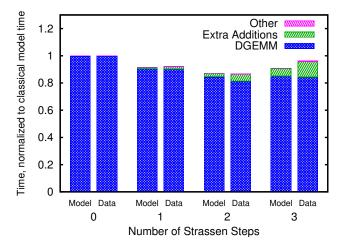

| 2.7  | Time breakdown comparison between the sequential model                                                                                                                                                                                         | $\frac{27}{27}$ |

| 2.8  | Comparison of the parallel model with the algorithms in strong scaling                                                                                                                                                                         | 29              |

| 2.9  | Time breakdown comparison between the parallel model and the data                                                                                                                                                                              | 29              |

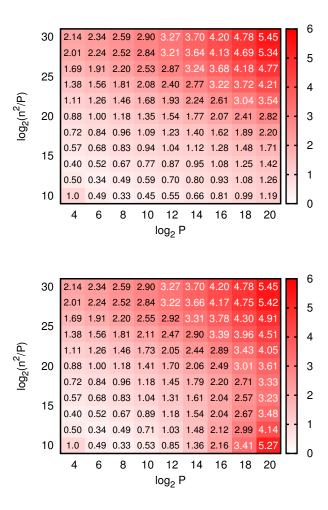

| 2.10 | Predicted speedups of CAPS over 2.5D and 2D on an exascale machine                                                                                                                                                                             | 30              |

| 2.11 | The memory and communication costs of all possible interleavings of BFS and                                                                                                                                                                    |                 |

|      | DFS steps                                                                                                                                                                                                                                      | 34              |

| 2.12 | Data layout for CAPS                                                                                                                                                                                                                           | 34              |

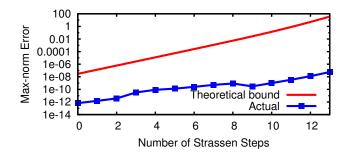

| 2.13 | Stability test: theoretical error bound versus actual error                                                                                                                                                                                    | 36              |

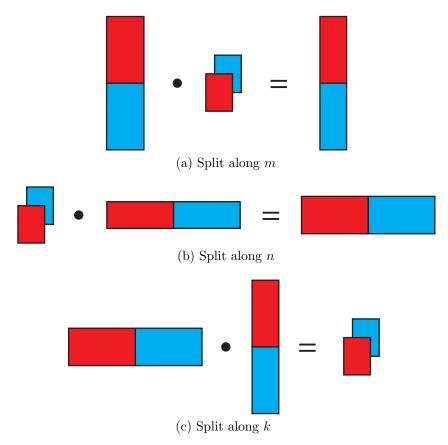

| 3.1  | Three ways to split rectangular matrix multiplication to get two subproblems                                                                                                                                                                   | 39              |

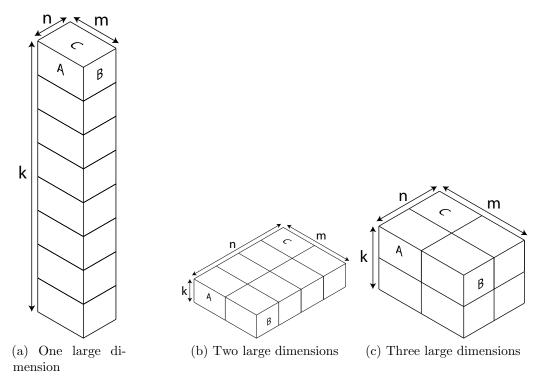

| 3.2  | Examples of the three cases of aspect ratios: one large dimension, two large                                                                                                                                                                   |                 |

|      | dimensions, and three large dimensions                                                                                                                                                                                                         | 41              |

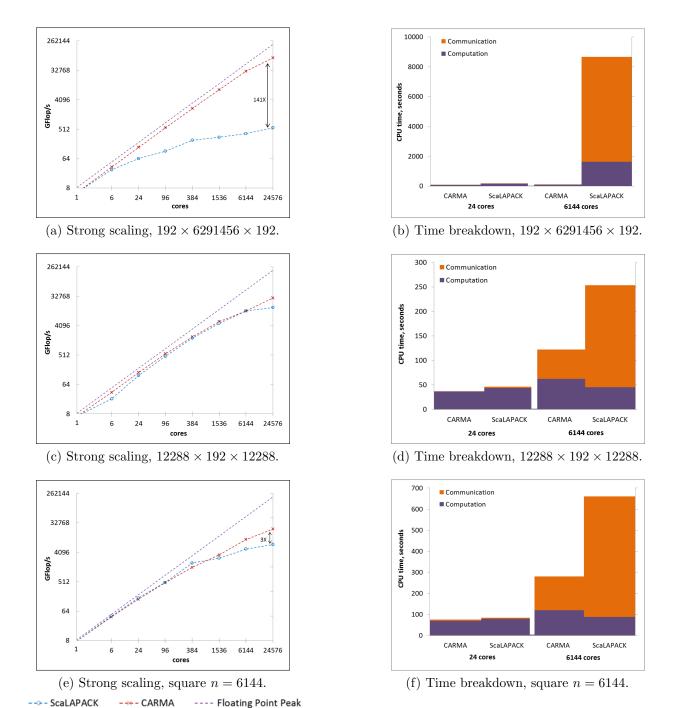

| 3.3  | CARMA compared to ScaLAPACK on Hopper                                                                                                                                                                                                          | 49              |

| 3.4  | Data layout for a BFS step                                                                                                                                                                                                                     | 53              |

| 4.1  | How the cube is partitioned in 1D, 2D, and 3D algorithms                                                                                                                                                                                       | 56              |

| 4.2  | Graphical representation of $V$ and $\ell_{ij}^C$                                                                                                                                                                                              | 57              |

| 4.3  | Two ways to split the matrix multiplication into four subproblems                                                                                                                                                                              | 62              |

| 4.4  | Strong scaling of sparse matrix multiplication                                                                                                                                                                                                 | 64              |

| 4.5  | Time breakdown for sparse matrix multiplication                                                                                                                                                                                                | 66              |

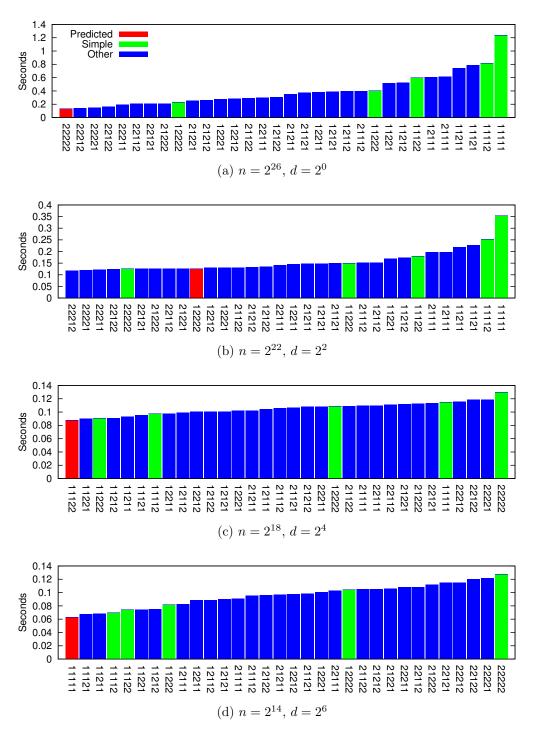

| 4.6  | Possible interleavings of the recursive algorithm                                                                                                                                                                                              | 67              |

## List of Tables

| 2.1 | Asymptotic computational and communication costs of Strassen-based and classi-            |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | cal square matrix multiplication algorithms and corresponding lower bounds                | 16 |

| 2.2 | The pattern of BFS and DFS steps and memory usage for CAPS                                | 23 |

| 2.3 | Asymptotic bandwidth costs of classical and fast, square and rectangular matrix           |    |

|     | mul tiplication                                                                           | 37 |

| 3.1 | Asymptotic bandwidth costs and lower bounds for rectangular matrix multiplication         | 44 |

| 4.1 | Asymptotic expected communication costs and lower bonuds for sparse matrix multiplication | 59 |

## Chapter 1

## Introduction

Matrix multiplication is one of the most fundamental algorithmic problems in numerical linear algebra, distributed computing, scientific computing, and high-performance computing. Parallelization of matrix multiplication has been extensively studied (e.g., [21, 12, 24, 2, 51, 39, 36, 23, 45, 61]). It has been addressed using many theoretical approaches, algorithmic tools, and software engineering methods in order to optimize performance and obtain faster and more efficient parallel algorithms and implementations.

To design efficient parallel algorithms, it is necessary not only to load balance the computation, but also to minimize the time spent communicating between processors. The interprocessor communication costs are in many cases significantly higher than the computational costs. Moreover, hardware trends predict that more problems will become communication-bound in the future [38, 35]. Even matrix multiplication, which is widely considered to be computation-bound, becomes communication-bound when a given problem is run on sufficiently many processors.

Here we consider three cases of matrix multiplication: fast matrix multiplication algorithms, such as Strassen's, which compute the product of dense matrices using asymptotically fewer than the naïve number of scalar products and so run in  $(o(n^3))$  time (Chapter 2); classical matrix multiplication, for which all of the naïve scalar products  $A_{ik} \cdot B_{ki}$  must be computed (Chapter 3); and sparse matrix multiplication, where most of the entries of the input matrices are zero, and only nonzero products are computed (Chapter 4). In each case, we present a new recursive parallel algorithm. The new algorithms are communication-optimal: they asymptotically match communication lower bounds, and they communicate asymptotically less than previous algorithms. In the cases of sparse matrix multiplication and high aspect ratio rectangular matrices for classical matrix multiplication we present new, tight lower bounds. We also present benchmarking data that shows our new algorithms are faster than previous algorithms in practice. Compared to the best previous algorithm, we show speedups of up to 2.8× for Strassen's algorithm, 140× for classical matrix multiplication, and 8× for sparse matrix multiplication. In Chapter 5, we explain how to generalize our parallelization approach to other recursive algorithms, including those with more dependencies than matrix multiplication.

#### 1.1 Communication Model

We model communication of distributed-memory parallel architectures as follows. We assume the machine has P processors, each with local memory of size M words, which are connected via a network. Processors communicate via messages, and we assume that a message of w words can be communicated in time  $\alpha + \beta w$ . Here  $\alpha$  and  $\beta$  are machine parameters specifying the overhead time per message and the reciprocal bandwidth, respectively. The bandwidth cost of the algorithm is given by the word count and denoted by W, and the latency cost is given by the message count and denoted by S. Similarly the computational cost is given by the number of floating point operations and denoted by F. We call the time per floating point operation  $\gamma$ .

We count the number of words, messages and floating point operations along the *critical* path as defined in [66]. That is, two messages that are communicated between separate pairs of processors simultaneously are counted only once, as are two floating point operations performed in parallel on different processors. Note that we do not require the communication to be bulk-synchronous: some of the processors may be engaged in communication while others are performing computations. This metric is closely related to the total running time of the algorithm, which we model as

$$\alpha S + \beta W + \gamma F$$

.

We assume that (1) the architecture is homogeneous (that is,  $\gamma$  is the same on all processors and  $\alpha$  and  $\beta$  are the same between each pair of processors), (2) processors can send/receive only one message to/from one processor at a time and they cannot overlap computation with communication (this latter assumption can be dropped, affecting the running time by a factor of at most two), and (3) there is no communication resource contention among processors. That is, we assume that there is a link in the network between each pair of processors. Thus lower bounds derived in this model are valid for any network, but attainability of the lower bounds depends on the details of the network. One way to model more realistic networks is as a hierarchy with different values for  $\alpha$  and  $\beta$  at each level.

## Perfect Strong Scaling

We say that an algorithm exhibits perfect strong scaling if its running time for a fixed problem size decreases linearly with the number of processors; that is, if all three of F, W, and S decrease linearly with P. Several of the algorithms we will discuss exhibit perfect strong scaling within certain ranges. Our running time model naturally generalizes to give an energy model, and perfect strong scaling of runtime corresponds to getting linear speedup in P while using no extra energy [32].

## 1.2 Iterative Parallel Matrix Multiplication Algorithms

The first scalable algorithm for parallel matrix multiplication is due to Cannon in 1969 [21]. Cannon's algorithm multiplies two  $n \times n$  matrices on P processors on a square grid with bandwidth cost  $O\left(n^2/\sqrt{P}\right)$ . SUMMA generalizes this to arbitrary matrix dimensions and a rectangular grid of processors [36] using broadcasts rather than cyclic shifts. We call these "2D" algorithms, because they use a two-dimensional processor grid and have bandwidth cost that scales as  $1/\sqrt{P}$ .

Another class of algorithms, known as "3D" [12, 2] because the communication pattern maps to a three-dimensional processor grid, uses more local memory and reduces communication relative to 2D algorithms. The bandwidth cost of these algorithms scales as  $1/P^{2/3}$ . Unfortunately, they can only be used if a factor of  $\Omega(P^{1/3})$  extra memory is available.

The "2.5D" algorithm [52, 61] interpolates between 2D and 3D algorithms, using as much memory as is available to reduce communication. For square matrices, it asymptotically matches the lower bounds of [45] and [5], and so is communication-optimal. The recently proposed 3D-SUMMA algorithm [57] attempts to generalize the 2.5D algorithm to rectangular matrices. As our communication lower bounds in Section 3.1 show, 3D-SUMMA is communication-optimal for many, but not all, matrix dimensions.

## 1.3 Parallelizing Recursive Algorithms

An alternative to the iterative parallelization approach is what we call the BFS/DFS approach. BFS/DFS algorithms are based on sequential recursive algorithms, and view the processor layout as a hierarchy rather than a grid. Breadth-first steps (BFS) and depth-first steps (DFS) are alternate ways to solve the subproblems. At a BFS step, all of the subproblems are solved in parallel on independent subsets of the processors, whereas at a DFS all the processors work together to solve the subproblems serially. In general, BFS steps reduce communication costs, but may require extra memory relative to DFS steps. The extra memory at a BFS step is because each subset of the processors must have space for the entire input and output of its subproblem. With correct interleaving of BFS and DFS steps to stay within the available memory, we show that BFS/DFS gives communication-optimal algorithms for all the cases of matrix multiplication we consider. Because of their recursive structure, BFS/DFS algorithms are cache-, processor-, and network-oblivious in the sense of [34, 13, 25, 26]. Note that they are not oblivious to the aggregated local memory (DRAM) size, which is necessary to determine the optimal interleaving of BFS and DFS steps. Hence they should perform well without much tuning on hierarchical architectures, which are becoming more common.

Our primary focus is on matrix multiplication algorithms. In this case, subproblems are independent of each other, and hence may be computed simultaneously. In Chapter 5, we relax

this requirement, and show how to parallelize some recursive algorithms with dependencies between the subproblems.

## 1.4 The Loomis-Whitney Inequality

The lower bound proofs in Sections 3.1 and 4.2 make use of the geometric embedding techniques of [45, 10], so we review them here. This section may be safely skipped if the reader is only interested in parallelizing Strassen's fast matrix multiplication algorithm as described in Chapter 2.

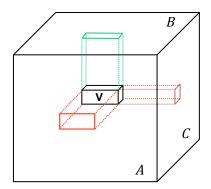

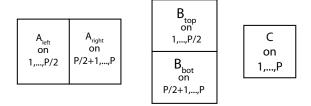

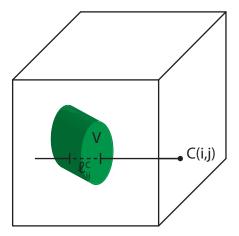

Let A be an  $m \times k$  matrix, B be a  $k \times n$  matrix, and C be an  $m \times n$  matrix. The mnk scalar multiplications that the classical algorithm performs when computing  $C = A \cdot B$  may be arranged into a rectangular prism  $\mathcal{V}$  of size  $m \times n \times k$  with the three matrices as its faces. To perform a given multiplication, a processor must have access to the entries of A, B, and C corresponding to the projections onto the  $m \times k$ ,  $n \times k$ , and  $m \times n$  faces of the prism, respectively. If these entries are not assigned to that processor by the initial or final data layout, these entries correspond to words that must be communicated.

Given a set of voxels  $V \subset \mathcal{V}$ , the projections of the set onto three orthogonal faces corresponds to the input elements of A and B necessary to perform the multiplications and the output elements of C that the products must update. The computation cube and this relationship of voxels to input and output matrix elements is shown in Figure 1.1. The following lemma relates the volume of V to its projections:

**Lemma 1.1.** [49] Let V be a finite set of lattice points in  $\mathbb{R}^3$ , i.e., points (x,y,z) with integer coordinates. Let  $V_x$  be the projection of V in the x-direction, i.e., all points (y,z) such that there exists an x so that  $(x,y,z) \in V$ . Define  $V_y$  and  $V_z$  similarly. Let  $|\cdot|$  denote the cardinality of a set. Then  $|V| \leq \sqrt{|V_x| \cdot |V_y| \cdot |V_z|}$ .

Figure 1.1: The computation rectangular prism for matrix multiplication, with a specified subset of voxels V along with its three projections. Each voxel corresponds to the multiplication of its projection onto A and B, and contributes to its projection onto C.

## Chapter 2

## Strassen's Matrix Multiplication

Strassen showed that  $2 \times 2$  matrix multiplication can be performed using 7 multiplications and 18 additions, instead of the classical algorithm that does 8 multiplications and 4 additions [62]. By recursive application this yields an algorithm which multiplies two  $n \times n$  matrices with  $O(n^{\omega_0})$  flops, where  $\omega_0 = \log_2 7 \approx 2.81$ . Winograd improved the algorithm to use 7 multiplications and 15 additions in the base case, thus decreasing the hidden constant in the O notation [65]. Further reduction in the number of additions is not possible [56, 16].

In this chapter, we show how to parallelize Strassen's algorithm in a communication-optimal way, and benchmark and analyze its performance on several machines. The results in this chapter are joint work with Grey Ballard, James Demmel, Olga Holtz, and Oded Schwartz. The algorithm, analysis, and preliminary performance appear in [6]; more performance results, implementation details, and performance modeling appear in [48].

We use the term parallel Strassen algorithm for a parallel algorithm that performs exactly the same arithmetic operations as any variant of Strassen's (sequential) algorithm; that is, any algorithm based on  $2 \times 2$  matrix multiplication using 7 scalar multiplications. We use the broader term parallel Strassen-based algorithm for a parallel matrix multiplication algorithm that is a hybrid of any variant of Strassen's and the classical algorithm. Examples of such hybrids are given in the next section. Note that Theorems 2.1 and 2.2 below apply to parallel Strassen algorithms, but not to all Strassen-based algorithms.

The rest of this chapter is organized as follows. We review the Strassen-Winograd algorithm in Section 2.1, and the communication-cost lower bounds for Strassen-like algorithms in Section 2.2. Section 2.3 presents our new communication-optimal algorithm. In Section 2.4 we analyze the communication costs of other approaches to parallelizing Strassen's algorithm, and show that none of them are communication-optimal. We present performance results for both classical and Strassen-based algorithms in Section 2.5 and compare the performance to a theoretical model in Section 2.6. We discuss details of our implementation, and numerical stability of Strassen's algorithm in Sections 2.7 and 2.8, respectively. Finally, in Section 2.9 we show how to generalize our approach to other fast matrix multiplication algorithms.

## 2.1 Strassen-Winograd Algorithm

To perform matrix multiplication using the Strassen-Winograd algorithm, first divide the input matrices A, B and output matrix C into 4 submatrices:

$$A = \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix} B = \begin{bmatrix} B_{11} & B_{12} \\ B_{21} & B_{22} \end{bmatrix} C = \begin{bmatrix} C_{11} & C_{12} \\ C_{21} & C_{22} \end{bmatrix}$$

Then compute 7 linear combinations of the submatrices of each of A and B, call these  $T_i$  and  $S_i$ , respectively; multiply them pairwise; then compute the submatrices of C as linear combinations of these products:

This is one step of Strassen-Winograd. The algorithm is recursive since it can be used for each of the 7 smaller matrix multiplications. In practice, one often uses only a few steps of Strassen-Winograd, although to attain  $O(n^{\omega_0})$  computational cost, it is necessary to recursively apply it all the way down to matrices of size  $O(1) \times O(1)$ . The precise computational cost of Strassen-Winograd is

$$F(n) = c_s n^{\omega_0} - 5n^2. (2.1)$$

Here  $c_s$  is a constant depending on the cutoff point at which one switches to the classical algorithm. For a cutoff size of  $n_0$ , the constant is  $c_s = (2n_0 + 4)/n_0^{\omega_0 - 2}$  which is minimized at  $n_0 = 8$  yielding a computational cost of approximately  $3.73n^{\omega_0} - 5n^2$ .

## 2.2 Communication Lower Bounds

For parallel Strassen algorithms, the bandwidth cost lower bound has been proved using expansion arguments on the computation graph [9], and the latency cost lower bound is an immediate corollary. We believe the requirement of no recomputation is purely technical, but there is no known proof of the lower bounds without it.

**Theorem 2.1.** (Memory-dependent lower bound) [9] Consider a parallel Strassen algorithm running on P processors each with local memory size M. Let W(n, P, M) be the bandwidth cost and S(n, P, M) be the latency cost of the algorithm. Assume that no intermediate values are computed twice. Then

$$W(n, P, M) = \Omega\left(\left(\frac{n}{\sqrt{M}}\right)^{\omega_0} \cdot \frac{M}{P}\right),$$

$$S(n, P, M) = \Omega\left(\left(\frac{n}{\sqrt{M}}\right)^{\omega_0} \cdot \frac{1}{P}\right).$$

We extended this to a memory-independent lower bound using the same expansion approach:

**Theorem 2.2.** (Memory-independent lower bound) [5] Consider a parallel Strassen algorithm running on P processors. Let W(n, P) be the bandwidth cost and S(n, P) be the latency cost of the algorithm. Assume that no intermediate values are computed twice. Assume only one copy of the input data is stored at the start of the algorithm and the computation is load-balanced in an asymptotic sense. Then

$$W(n, P) = \Omega\left(\frac{n^2}{P^{2/\omega_0}}\right),$$

$$S(n, P) = \Omega(1).$$

Note that when  $M = O(n^2/P^{2/\omega_0})$ , the memory-dependent lower bound dominates, and when  $M = \Omega(n^2/P^{2/\omega_0})$ , the memory-independent lower bound dominates.

## 2.3 Communication-Avoiding Parallel Strassen

In this section we present the CAPS algorithm, and prove it is communication-optimal. See Algorithm 1 for a concise presentation and Algorithm 2 for a more detailed description.

Theorem 2.3. CAPS has computational cost

$$\Theta\left(\frac{n^{\omega_0}}{P}\right),$$

$bandwidth \ cost$

$$\Theta\left(\max\left\{\frac{n^{\omega_0}}{PM^{\omega_0/2-1}}, \frac{n^2}{P^{2/\omega_0}}\right\}\right),\,$$

and latency cost

$$\Theta\left(\max\left\{\frac{n^{\omega_0}}{PM^{\omega_0/2}}\log P, \log P\right\}\right).$$

By Theorems 2.1 and 2.2, we see that CAPS has optimal computational and bandwidth costs, and that its latency cost is at most  $\log P$  away from optimal. We prove Theorem 2.3 in Section 2.3.5.

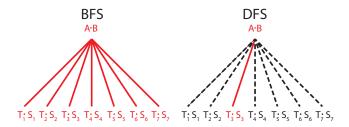

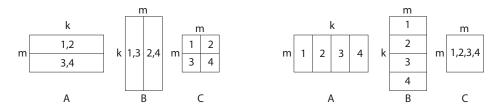

Figure 2.1: Representation of BFS and DFS steps. In a BFS step, all seven subproblems are computed at once, each on 1/7 of the processors. In a DFS step, the seven subproblems are computed in sequence, each using all the processors. The notation follows that of Section 2.1.

#### 2.3.1 Overview of CAPS

Consider the recursion tree of Strassen's sequential algorithm. CAPS traverses it in parallel as follows. At each level of the tree, the algorithm proceeds in one of two ways. A "breadth-first-step" (BFS) divides the 7 subproblems among the processors, so that  $\frac{1}{7}$  of the processors work on each subproblem independently and in parallel. A "depth-first-step" (DFS) uses all the processors on each subproblem, solving each one in sequence. See Figure 2.1.

In short, a BFS step requires more memory but reduces communication costs while a DFS step requires little extra memory but is less communication-efficient. In order to minimize communication costs, the algorithm must choose an ordering of BFS and DFS steps that uses as much memory as possible.

Let  $k = \log_7 P$  and  $s \ge k$  be the number of distributed Strassen steps the algorithm will take. For simplicity, in this section, we assume that n is a multiple of  $2^s 7^{\lceil k/2 \rceil}$ . If k is even, the restriction simplifies to n being a multiple of  $2^s \sqrt{P}$ . Since P is a power of 7, it is sometimes convenient to think of the processors as numbered in base 7. CAPS performs s steps of Strassen's algorithm and finishes the calculation with local matrix multiplication. The algorithm can easily be generalized to other values of n by padding or dynamic peeling (where, at each recursive step, if the matrix dimension is odd the last row and column are handled separately).

We consider two simple schemes of traversing the recursion tree with BFS and DFS steps. The first scheme, which we call the Unlimited Memory (UM) scheme, is to take k BFS steps in a row. This approach is possible only if there is sufficient available memory. It is also used in the second scheme, which we call the Limited Memory (LM) scheme, which is to take  $\ell$  DFS steps in a row followed by k BFS steps in a row, where  $\ell$  is minimized subject to the memory constraints.

It is possible to use a more complicated scheme that interleaves BFS and DFS steps to reduce communication. We show that the LM scheme is optimal up to a constant factor, and hence no more than a constant factor improvement can be attained from interleaving.

#### **Algorithm 1** CAPS, in brief. For more details, see Algorithm 2.

```

Input: A, B, n, where A and B are n \times n matrices

P = \text{number of processors}

Output: C = A \cdot B

\triangleright The dependence of the S_i's on A, the T_i's on B and C on the Q_i's follows the Strassen

or Strassen-Winograd algorithm. See Section 2.1.

1: procedure C = CAPS(A, B, n, P)

if enough memory then

▷ Do a BFS step

2:

locally compute the S_i's and T_i's from A and B

3:

parallel for i = 1 \dots 7 do

4:

redistribute S_i and T_i

5:

Q_i = \text{CAPS}(S_i, T_i, n/2, P/7)

6:

redistribute Q_i

7:

locally compute C from all the Q_i's

8:

else

▷ Do a DFS step

9:

10:

for i = 1 \dots 7 do

locally compute S_i and T_i from A and B

11:

Q_i = CAPS(S_i, T_i, n/2, P)

12:

locally compute contribution of Q_i to C

13:

```

## 2.3.2 Data layout

We require that the data layout of the matrices satisfies the following two properties:

- 1. At each of the s Strassen recursion steps, the data layouts of the four sub-matrices of each of A, B, and C must match so that the weighted additions of these sub-matrices can be performed locally. This technique follows [51] and allows communication-free DFS steps.

- 2. Each of these submatrices must be equally distributed among the *P* processors for load balancing.

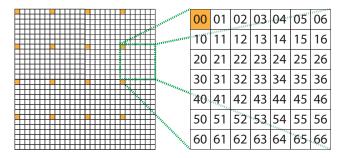

There are many data layouts that satisfy these properties, perhaps the simplest being block-cyclic layout with a processor grid of size  $7^{\lfloor k/2 \rfloor} \times 7^{\lceil k/2 \rceil}$  and block size  $\frac{n}{2^s 7^{\lfloor k/2 \rfloor}} \times \frac{n}{2^s 7^{\lceil k/2 \rceil}}$ . (When  $k = \log_7 P$  is even these expressions simplify to a processor grid of size  $\sqrt{P} \times \sqrt{P}$  and block size  $\frac{n}{2^s \sqrt{P}}$ .) See Figure 2.2.

Any layout that we use is specified by three parameters, (n, P, s), and intermediate stages of the computation use the same layout with smaller values of the parameters. A BFS step reduces a multiplication problem with layout parameters (n, P, s) to seven subproblems with layout parameters (n/2, P/7, s-1). A DFS step reduces a multiplication problem with layout parameters (n, P, s) to seven subproblems with layout parameters (n/2, P, s-1).

Note that if the input data is initially load-balanced but distributed using a different layout, we can rearrange it to the above layout using no more than  $O\left(\frac{n^2}{P}\right)$  words and O(P) messages. This has no asymptotic effect on the bandwidth cost but may significantly increase the latency cost.

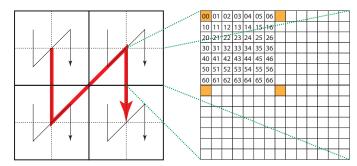

Figure 2.2: An example matrix layout for CAPS. Each of the 16 submatrices as shown on the left has exactly the same layout. The colored blocks are the ones owned by processor 00. On the right is a zoomed-in view of one submatrix, showing which processor, numbered base 7, owns each block. This is block-cyclic layout with some blocksize b, and matches our layout requirements with parameters  $(n = 4 \cdot 7 \cdot b, P = 49, s = 2)$ .

### 2.3.3 Unlimited Memory (UM) scheme

In the UM scheme, we take  $k = \log_7 P$  BFS steps in a row. Since a BFS step reduces the number of processors involved in each subproblem by a factor of 7, after k BFS steps each subproblem is assigned to a single processor, and so is computed locally with no further communication costs. We first describe a BFS step in more detail.

The matrices A and B are initially distributed as described in Section 2.3.2. In order to take a recursive step, the 14 matrices  $S_1, \ldots, S_7, T_1, \ldots, T_7$  must be computed. Each processor allocates space for all 14 matrices and performs local additions and subtractions to compute its portion of the matrices. Recall that the submatrices are distributed identically, so this step requires no communication. If the layouts of A and B have parameters (n, P, s), the  $S_i$  and the  $T_i$  now have layout parameters (n/2, P, s-1).

The next step is to redistribute these 14 matrices so that the 7 pairs of matrices  $(S_i, T_i)$  exist on disjoint sets of P/7 processors. This requires disjoint sets of 7 processors performing an all-to-all communication step (each processor must send and receive a message from each of the other 6). To see this, consider the numbering of the processors base-7. On the  $m^{\text{th}}$  BFS step, the communication is between the seven processors whose numbers agree on all digits except the  $m^{\text{th}}$  (counting from the right). After the  $m^{\text{th}}$  BFS step, the set of processors working on a given subproblem share the same m-digit suffix. After the above communication is performed, the layout of  $S_i$  and  $T_i$  has parameters (n/2, P/7, s-1), and the sets of processors that own the  $T_i$  and  $S_i$  are disjoint for different values of i. Since each all-to-all

#### **Algorithm 2** CAPS, in detail

```

Input: A, B, are n \times n matrices

P = \text{number of processors}

rank = processor number base-7 as an array

M = local memory size

Output: C = A \cdot B

1: procedure C = CAPS(A, B, P, rank, M)

\ell = \left\lceil \log_2 \frac{4n}{P^{1/\omega_0} M^{1/2}} \right\rceil

\triangleright \ell is number of DFS steps to fit in memory

k = \log_7 P

3:

call DFS(A, B, C, k, \ell, rank)

4:

1: procedure DFS(A, B, C, k, \ell, rank)

\triangleright Do C = A \cdot B by \ell DFS, then k BFS steps

if \ell \leq 0 then call BFS( A, B, C, k, rank); return

for i = 1 \dots 7 do

3:

locally compute S_i and T_i from A and B

4:

▶ following Strassen's algorithm

call DFS(S_i, T_i, Q_i, k, \ell - 1, \text{rank})

5:

locally compute contribution of Q_i to C

6:

▶ following Strassen's algorithm

1: procedure BFS(A, B, C, k, rank)

\triangleright Do C = A \cdot B by k BFS steps, then local Strassen

if k == 0 then call localStrassen(A, B, C); return

2:

for i = 1 \dots 7 do

3:

locally compute S_i and T_i from A and B

▶ following Strassen's algorithm

4:

for i = 1 \dots 7 do

5:

target = rank

6:

target[k] = i

7:

send S_i to target

8:

receive into L

\triangleright One part of L comes from each of 7 processors

9:

10:

send T_i to target

\triangleright One part of R comes from each of 7 processors

receive into R

11:

call BFS(L, R, V, k-1, rank)

12:

for i = 1 \dots 7 do

13:

target = rank

14:

target[k] = i

15:

send i^{\text{th}} part of V to target

16:

receive from target into Q_i

17:

locally compute C from Q_i

⊳ following Strassen's algorithm

18:

```

communication only involves seven processors no matter how large P is, this algorithm does not have the scalability issues that typically come from an all-to-all communication pattern.

#### Memory requirements

The extra memory required to take one BFS step is the space to store all 7 triples  $S_j$ ,  $T_j$ ,  $Q_j$ . Since each of those matrices is  $\frac{1}{4}$  the size of A, B, and C, the extra space required at a given step is 7/4 the extra space required for the previous step. We assume that no extra memory is required for the local multiplications. Thus, the total local memory requirement for taking k BFS steps is given by

$$\operatorname{Mem}_{\mathrm{UM}}(n,P) = \frac{3n^2}{P} \sum_{i=0}^{k} \left(\frac{7}{4}\right)^i = \frac{7n^2}{P^{2/\omega_0}} - \frac{4n^2}{P} = \Theta\left(\frac{n^2}{P^{2/\omega_0}}\right).$$

#### Computational costs

The computation required at a given BFS step is that of the local additions and subtractions associated with computing the  $S_i$  and  $T_i$  and updating the output matrix C with the  $Q_i$ . Since Strassen-Winograd performs 15 additions and subtractions, the computational cost recurrence is

$$F_{\text{UM}}(n,P) = 15\left(\frac{n^2}{4P}\right) + F_{\text{UM}}\left(\frac{n}{2},\frac{P}{7}\right)$$

with base case  $F_{\text{UM}}(n,1) = c_s n^{\omega_0} - 5n^2$ , where  $c_s$  is the constant of Strassen-Winograd. See Section 2.1 for more details. The solution to this recurrence is

$$F_{\text{UM}}(n, P) = \frac{c_s n^{\omega_0} - 5n^2}{P} = \Theta\left(\frac{n^{\omega_0}}{P}\right).$$

#### Communication costs

Consider the communication costs associated with the UM scheme. Given that the redistribution within a BFS step is performed by an all-to-all communication step among sets of 7 processors, each processor sends 6 messages and receives 6 messages to redistribute  $S_1, \ldots, S_7$ , and the same for  $T_1, \ldots, T_7$ . After the products  $Q_i = S_i T_i$  are computed, each processor sends 6 messages and receives 6 messages to redistribute  $Q_1, \ldots, Q_7$ . The size of each message varies according to the recursion depth, and is the number of words a processor owns of any  $S_i$ ,  $T_i$ , or  $Q_i$ , namely  $\frac{n^2}{4P}$  words.

<sup>&</sup>lt;sup>1</sup>If one does not overwrite the input, it is impossible to run Strassen in place; however using a few temporary matrices affects the analysis here by a constant factor only.

As each of the  $Q_i$  is computed simultaneously on disjoint sets of P/7 processors, we obtain a cost recurrence for the entire UM scheme:

$$W_{\text{UM}}(n, P) = 36 \frac{n^2}{4P} + W_{\text{UM}} \left(\frac{n}{2}, \frac{P}{7}\right)$$

$S_{\text{UM}}(n, P) = 36 + S_{\text{UM}} \left(\frac{n}{2}, \frac{P}{7}\right)$

with base case  $S_{\text{UM}}(n,1) = W_{\text{UM}}(n,1) = 0$ . Thus

$$W_{\text{UM}}(n, P) = \frac{12n^2}{P^{2/\omega_0}} - \frac{12n^2}{P} = \Theta\left(\frac{n^2}{P^{2/\omega_0}}\right)$$

$$S_{\text{UM}}(n, P) = 36\log_7 P = \Theta\left(\log P\right). \tag{2.2}$$

### 2.3.4 Limited Memory (LM) scheme

In this section we discuss a scheme for traversing Strassen's recursion tree in the context of limited memory. In the LM scheme, we take  $\ell$  DFS steps in a row followed by k BFS steps in a row, where  $\ell$  is minimized subject to the memory constraints. That is, we use a sequence of DFS steps to reduce the problem size so that we can use the UM scheme on each subproblem without exceeding the available memory.

Consider taking a single DFS step. Rather than allocating space for and computing all 14 matrices  $S_1, T_1, \ldots, S_7, T_7$  at once, the DFS step requires allocation of only one subproblem, and each of the  $Q_i$  will be computed in sequence.

Consider the  $i^{th}$  subproblem: as before, both  $S_i$  and  $T_i$  can be computed locally. After  $Q_i$  is computed, it is used to update the corresponding quadrants of C and then discarded so that its space in memory (as well as the space for  $S_i$  and  $T_i$ ) can be re-used for the next subproblem. In a DFS step, no redistribution occurs. After  $S_i$  and  $T_i$  are computed, all processors participate in the computation of  $Q_i$ .

We assume that some extra memory is available. To be precise, assume the matrices A, B, and C require only  $\frac{1}{3}$  of the available memory:

$$\frac{3n^2}{P} \le \frac{1}{3}M. \tag{2.3}$$

In the LM scheme, we set

$$\ell = \max\left\{0, \left\lceil \log_2 \frac{4n}{P^{1/\omega_0} M^{1/2}} \right\rceil\right\}. \tag{2.4}$$

The following subsection shows that this choice of  $\ell$  is sufficient not to exceed the memory capacity.

#### Memory requirements

The extra memory requirement for a DFS step is the space to store one subproblem. Thus, the extra space required at this step is 1/4 the space required to store A, B, and C. The local memory requirements for the LM scheme is given by

$$\operatorname{Mem}_{\operatorname{LM}}(n,P) = \frac{3n^2}{P} \sum_{i=0}^{\ell-1} \left(\frac{1}{4}\right)^i + \operatorname{Mem}_{\operatorname{UM}}\left(\frac{n}{2^{\ell}},P\right)$$

$$\leq \frac{M}{3} \sum_{i=0}^{\ell-1} \left(\frac{1}{4}\right)^i + \frac{7\left(\frac{n}{2^{\ell}}\right)^2}{P^{2/\omega_0}}$$

$$\leq \frac{127}{144} M < M,$$

where the last line follows from (2.4) and (2.3). Thus, the limited memory scheme does not exceed the available memory.

#### Computational costs

As in the UM case, the computation required at a given DFS step is that of the local additions and subtractions associated with computing each  $S_i$  and  $T_i$  and updating the output matrix C with the  $Q_i$ . However, since all processors participate in each subproblem and the subproblems are computed in sequence, the recurrence is given by

$$F_{\rm LM}(n,P) = 15\left(\frac{n^2}{4P}\right) + 7 \cdot F_{\rm LM}\left(\frac{n}{2},P\right).$$

After  $\ell$  steps of DFS, the size of a subproblems is  $\frac{n}{2^{\ell}} \times \frac{n}{2^{\ell}}$ , and there are P processors involved. We take k BFS steps to compute each of these  $7^{\ell}$  subproblems. Thus

$$F_{\text{LM}}\left(\frac{n}{2^{\ell}}, P\right) = F_{\text{UM}}\left(\frac{n}{2^{\ell}}, P\right),$$

and

$$F_{\rm LM}\left(n,P\right) = \frac{15n^2}{4P} \sum_{i=0}^{\ell-1} \left(\frac{7}{4}\right)^i + 7^{\ell} \cdot F_{\rm UM}\left(\frac{n}{2^{\ell}},P\right) = \frac{c_s n^{\omega_0} - 5n^2}{P} = \Theta\left(\frac{n_0^{\omega}}{P}\right).$$

#### Communication costs

Since there are no communication costs associated with a DFS step, the recurrence is simply

$$W_{\rm LM}(n,P) = 7 \cdot W_{\rm LM}\left(\frac{n}{2},P\right)$$

$$S_{\rm LM}(n,P) = 7 \cdot S_{\rm LM}\left(\frac{n}{2},P\right)$$

with base cases

$$W_{\rm LM}\left(\frac{n}{2^{\ell}},P\right) = W_{\rm UM}\left(\frac{n}{2^{\ell}},P\right)$$

$$S_{\rm LM}\left(\frac{n}{2^{\ell}},P\right) = S_{\rm UM}\left(\frac{n}{2^{\ell}},P\right).$$

Thus the total communication costs are given by

$$W_{\text{LM}}(n, P) = 7^{\ell} \cdot W_{\text{UM}}\left(\frac{n}{2^{\ell}}, P\right) \le \frac{12 \cdot 4^{\omega_0 - 2} n^{\omega_0}}{P M^{\omega_0/2 - 1}} = \Theta\left(\frac{n^{\omega_0}}{P M^{\omega_0/2 - 1}}\right).$$

$$S_{\text{LM}}(n, P) = 7^{\ell} \cdot S_{\text{UM}}\left(\frac{n}{2^{\ell}}, P\right) \le \frac{(4n)^{\omega_0}}{P M^{\omega_0/2}} 36 \log_7 P = \Theta\left(\frac{n^{\omega_0}}{P M^{\omega_0/2}} \log P\right). \tag{2.5}$$

#### 2.3.5 Communication optimality

Proof. (of Theorem 2.3 on page 7). In the case that  $M \geq \operatorname{Mem}_{\operatorname{UM}}(n,P) = \Omega\left(\frac{n^2}{P^{2/\omega_0}}\right)$  the UM scheme is possible. Then the communication costs are given by Equation (2.2) on page 13 which matches the lower bound of Theorem 2.2 on page 7. Thus the UM scheme is communication-optimal (up to a logarithmic factor in the latency cost and assuming that the data is initially distributed as described in Section 2.3.2). For smaller values of M, the LM scheme must be used. Then the communication costs are given by Equation (2.5) on page 15 and match the lower bound of Theorem 2.1 on page 6, so the LM scheme is also communication-optimal.

We note that for the LM scheme, since both the computational and communication costs are proportional to  $\frac{1}{P}$  (up to a log P factor on S), we can expect perfect strong scaling: given a fixed problem size, increasing the number of processors by some factor will decrease each cost by the same factor. However, this strong scaling property has a limited range. For any fixed M and n, increasing P increases the global memory size PM. The limit of perfect strong scaling is exactly when there is enough memory for the UM scheme. See [5] for details.

## 2.4 Analysis of Other Algorithms

In this section we detail the asymptotic communication costs of other matrix multiplication algorithms, both classical and Strassen-based. These communication costs and the corresponding lower bounds are summarized in Table 2.1.

Many of the algorithms described in this section are hybrids of two different algorithms. We use the convention that the names of the hybrid algorithms are composed of the names of the two component algorithms, hyphenated. The first name describes the algorithm used at the top level, on the largest problems, and the second describes the algorithm used at the base level on smaller problems.

|        |                           | Flops                                                                                     | Bandwidth                                                                                                                      | Latency                                                                  |

|--------|---------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|        | Lower Bound [5, 45]       | $\frac{n^3}{P}$                                                                           | $\max\left\{\frac{n^3}{PM^{1/2}}, \frac{n^2}{P^{2/3}}\right\}$                                                                 | $\max\left\{\frac{n^3}{PM^{3/2}},1\right\}$                              |

| ssical | 2D [21, 36]               | $\frac{n^3}{P}$                                                                           | $\frac{n^2}{P^{1/2}}$                                                                                                          | $p^{1/2}$                                                                |

| CISS   | 3D [2, 12]                | $\frac{n^3}{P}$                                                                           | $\frac{n^2}{P^{2/3}}$                                                                                                          | $\log P$                                                                 |

|        | 2.5D [52, 61], CARMA [31] | $\frac{n^3}{P}$                                                                           | $\max\left\{\frac{n^3}{PM^{1/2}}, \frac{n^2}{P^{2/3}}\right\}$                                                                 | $\frac{n^3}{PM^{3/2}} + \log P$                                          |

|        | Lower Bound [5, 9]        | $\frac{n^{\omega_0}}{P}$                                                                  | $\max\left\{\frac{n^{\omega_0}}{PM^{\omega_0/2-1}}, \frac{n^2}{P^{2/\omega_0}}\right\}$                                        | $\max\left\{\frac{n^{\omega_0}}{PM^{\omega_0/2}},1\right\}$              |

|        | 2D-Strassen [51]          | $\frac{n^{\omega_0}}{P^{(\omega_0-1)/2}}$                                                 | $\frac{n^2}{\overline{P^{1/2}}}$                                                                                               | $P^{1/2}$                                                                |

| uəssı  | Strassen-2D [39, 51]      | $\left(\frac{7}{8}\right)^{\ell} \frac{n^3}{P}$                                           | $\left(\frac{7}{4}\right)^{\ell} \frac{n^2}{P^{1/2}}$                                                                          | $7^\ell P^{1/2}$                                                         |

| srtZ   | 2.5D-Strassen [6]         | $\max\left\{\frac{n^3}{PM^{3/2-\omega_0/2}}, \frac{n^{\omega_0}}{P^{\omega_0/3}}\right\}$ | $\max\left\{\frac{n^3}{PM^{1/2}}, \frac{n^2}{P^{2/3}}\right\}$                                                                 | $\frac{n^3}{PM^{3/2}} + \log P$                                          |

|        | Strassen-2.5D [6]         | $\left(\frac{7}{8}\right)^{\ell} \frac{n^3}{P}$                                           | $\max\left\{\left(\frac{7}{8}\right)^{\ell} \frac{n^3}{PM^{1/2}}, \left(\frac{7}{4}\right)^{\ell} \frac{n^2}{P^{2/3}}\right\}$ | $\left(\frac{7}{8}\right)^{\ell} \frac{n^3}{PM^{3/2}} + 7^{\ell} \log P$ |

|        | CAPS [6]                  | $\frac{n^{\omega_0}}{P}$                                                                  | $\max\left\{\frac{n^{\omega_0}}{PM^{\omega_0/2-1}}, \frac{n^2}{P^{2/\omega_0}}\right\}$                                        | $\max\left\{\frac{n^{\omega_0}}{PM^{\omega_0/2}}\log P, \log P\right\}$  |

Table 2.1: Asymptotic computational and communication costs of Strassen-basend and classical square matrix multiplication algorithms and corresponding lower bounds. Here  $\omega_0 = \log_2 7 \approx 2.81$  is the exponent of Strassen;  $\ell$  is the number of Strassen steps taken. The CAPS algorithm attains the lower bounds of Section 2.2, and thus is optimal. All of the other Strassen-based algorithms have asymptotically higher communication costs; see Section 2.4 for details.

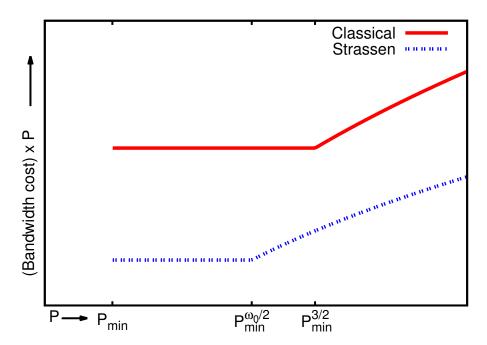

### 2.4.1 Classical Algorithms

Any classical algorithm must communicate asymptotically more than an optimal parallel Strassen algorithm (see the lower bounds in [45]). To compare the communication cost upper and lower bounds of classical and parallel Strassen algorithms, it is necessary to consider three cases for the memory size: when the memory-dependent bounds dominate for both classical and Strassen, when the memory-dependent bound dominates for classical but the memory-independent bound dominates for Strassen, and when the memory-independent bounds dominate for both classical and Strassen. See Figure 2.3.

Case 1  $M = \Omega(n^2/P)$  and  $M = O(n^2/P^{2/\omega_0})$ . The first condition is necessary for there to be enough memory to hold the input and output matrices; the second condition puts both classical and Strassen algorithms in the memory-dependent case. Then the ratio of the bandwidth costs is:

$$R = \Theta\left(\frac{n^3}{PM^{1/2}} / \frac{n^{\omega_0}}{PM^{\omega_0/2 - 1}}\right) = \Theta\left(\left(\frac{n^2}{M}\right)^{(3 - \omega_0)/2}\right).$$

Using the two bounds that define this case, we obtain  $R = O(P^{(3-\omega_0)/2})$  and  $R = \Omega(P^{3/\omega_0-1})$ .

Case 2  $M = \Omega(n^2/P^{2/\omega_0})$  and  $M = O(n^2/P^{2/3})$ . This means that in the classical case the memory-dependent lower bound dominates, but in the Strassen case the memory-independent lower bound dominates. Then the ratio is:

$$R = \Theta\left(\frac{n^3}{PM^{1/2}} / \frac{n^2}{P^{2/\omega_0}}\right) = \Theta\left(\left(\frac{n^2}{M}\right)^{1/2} P^{2/\omega_0 - 1}\right).$$

Using the two bounds that define this case, we obtain  $R = O(P^{3/\omega_0 - 1})$  and  $R = \Omega(P^{2/\omega_0 - 2/3})$ .

Case 3  $M = \Omega(P^{2/3})$ . This means that both the classical and Strassen lower bounds are dominated by the memory-independent cases. Then the ratio is:

$$R = \Theta\left(\frac{n^2}{P^{2/3}} / \frac{n^2}{P^{2/\omega_0}}\right) = \Theta\left(P^{2/\omega_0 - 2/3}\right).$$

Overall, depending on the ratio of the problem size to the available memory, the factor by which the classical bandwidth costs exceed the Strassen bandwidth costs is  $\Theta(P^a)$ , where a ranges from  $\frac{2}{\omega_0} - \frac{2}{3} \approx 0.046$  to  $\frac{3-\omega_0}{2} \approx 0.10$ . The same sort of analysis is used throughout Section 2.4 to compare each algorithm with the parallel Strassen lower bounds.

Figure 2.3: Bandwidth costs and strong scaling of matrix multiplication: classical vs. Strassenbased. Horizontal lines correspond to perfect strong scaling.  $P_{\min}$  is the minimum number of processors required to store the input and output matrices.

#### 2.4.2 2D-Strassen

One idea to construct a parallel Strassen-based algorithm is to use a 2D classical algorithm for the inter-processor communication, and use the fast matrix multiplication algorithm locally [51]. We call such an algorithm "2D-Strassen". It is straightforward to implement, but cannot attain all the computational speedup from Strassen since it uses a classical algorithm for part of the computation. In particular, it does not use Strassen for the largest matrices, when Strassen would provide the greatest reduction in computation. As a result, the computational cost exceeds  $\Theta(n^{\omega_0}/P)$  by a factor of  $P^{(3-\omega_0)/2} \approx P^{0.10}$ . The 2D-Strassen algorithm has the same communication cost as 2D algorithms, and hence does not match the communication costs of CAPS. In comparing the 2D-Strassen bandwidth cost,  $\Theta(n^2/P^{1/2})$ , to the CAPS bandwidth cost in Section 2.3, note that for the problem to fit in memory we always have  $M = \Omega(n^2/P)$ . The bandwidth cost exceeds that of CAPS by a factor of  $P^a$ , where a ranges from  $(3 - \omega_0)/2 \approx .10$  to  $2/\omega_0 - 1/2 \approx .21$ , depending on the relative problem size. Similarly, the latency cost,  $\Theta(P^{1/2})$ , exceeds that of CAPS by a factor of  $P^a$  where a ranges from  $(3 - \omega_0)/2 \approx .10$  to 1/2 = .5.

#### 2.4.3 Strassen-2D

The "Strassen-2D" algorithm applies  $\ell$  DFS steps of Strassen's algorithm at the top level, and performs the  $7^{\ell}$  smaller matrix multiplications using a 2D algorithm. By choosing certain data layouts as in Section 2.3.2, it is possible to do the additions and subtractions for Strassen's algorithm without any communication [51]. However, Strassen-2D is also unable to match the communication costs of CAPS. Moreover, the speedup of Strassen-2D in computation comes at the expense of extra communication. For large numbers of Strassen steps  $\ell$ , Strassen-2D can approach the computational lower bound of Strassen, but each step increases the bandwidth cost by a factor of  $\frac{7}{4}$  and the latency cost by a factor of 7. Thus the bandwidth cost of Strassen-2D is a factor of  $(\frac{7}{4})^{\ell}$  higher than 2D-Strassen, which is already higher than that of CAPS. The latency cost is even worse: Strassen-2D is a factor of  $7^{\ell}$  higher than 2D-Strassen.

One can reduce the latency cost of Strassen-2D at the expense of a larger memory footprint. Since Strassen-2D runs a 2D algorithm  $7^{\ell}$  times on the same set of processors, it is possible to pack together messages from independent matrix multiplications. In the best case, the latency cost is reduced to the cost of 2D-Strassen, which is still above that of CAPS, at the expense of using a factor of  $\left(\frac{7}{4}\right)^{\ell}$  more memory.

#### 2.4.4 2.5D-Strassen

A natural idea is to replace a 2D classical algorithm in 2D-Strassen with the superior 2.5D classical algorithm to obtain an algorithm we call 2.5D-Strassen. This algorithm uses the 2.5D algorithm for the inter-processor communication, and then uses Strassen for the local computation. When  $M = \Theta(n^2/P)$ , 2.5D-Strassen is exactly the same as 2D-Strassen, but when there is extra memory it both decreases the communication cost and decreases the computational cost since the local matrix multiplications are performed (using Strassen) on larger matrices. To be precise, the computational cost exceeds the lower bound by a factor of  $P^a$  where a ranges from  $1 - \frac{\omega_0}{3} \approx 0.064$  to  $\frac{3-\omega_0}{2} \approx 0.10$  depending on the relative problem size. The bandwidth cost exceeds the bandwidth cost of CAPS by a factor of  $P^a$  where a ranges from  $\frac{2}{\omega_0} - \frac{2}{3} \approx 0.046$  to  $\frac{3-\omega_0}{2} \approx 0.10$ . In terms of latency, the cost of  $\frac{n^3}{PM^{3/2}} + \log P$  exceeds the latency cost of CAPS by a factor ranging from  $\log P$  to  $P^{(3-\omega_0)/2} \approx P^{0.10}$ , depending on the relative problem size.

#### 2.4.5 Strassen-2.5D

Similarly, by replacing a 2D algorithm with 2.5D in Strassen-2D, one obtains the new algorithm we call Strassen-2.5D. First one takes  $\ell$  DFS steps of Strassen, which can be done without communication, and then one applies the 2.5D algorithm to each of the  $7^{\ell}$  subproblems. The computational cost is exactly the same as Strassen-2D, but the communication cost will typically be lower. Each of the  $7^{\ell}$  subproblems is multiplication of  $n/2^{\ell} \times n/2^{\ell}$  matrices. Each subproblem uses only  $1/4^{\ell}$  as much memory as the original problem. Thus there may be a large amount of extra memory available for each subproblem, and the lower communication

costs of the 2.5D algorithm help. The choice of  $\ell$  that minimizes the bandwidth cost is

$$\ell_{\text{opt}} = \max\left\{0, \left\lceil \log_2 \frac{n}{M^{1/2} P^{1/3}} \right\rceil\right\}.$$

The same choice minimizes the latency cost. Note that when  $M \geq \frac{n^2}{P^{2/3}}$ , taking zero Strassen steps minimizes the communication within the constraints of the Strassen-2.5D algorithm. With  $\ell = \ell_{\rm opt}$ , the bandwidth cost is a factor of  $P^{1-\omega_0/3} \approx P^{0.064}$  above that of CAPS. Additionally, the computational cost is not optimal, and using  $\ell = \ell_{\rm opt}$ , the computational cost exceeds the optimal by a factor of  $P^{1-\omega_0/3}M^{3/2-\omega_0/2} \approx P^{0.064}M^{0.096}$ .

It is also possible to take  $\ell > \ell_{\rm opt}$  steps of Strassen to decrease the computational cost further. However the decreased computational cost comes at the expense of higher communication cost, as in the case of Strassen-2D. In particular, each extra step over  $\ell_{\rm opt}$  increases the bandwidth cost by a factor of  $\frac{7}{4}$  and the latency cost by a factor of 7. As with Strassen-2D, it is possible to use extra memory to pack together messages from several subproblems and decrease the latency cost, but not the bandwidth cost.

### 2.5 Performance Results

We have implemented CAPS using MPI on three supercomputers, a Cray XE6 (Hopper<sup>2</sup>), an IBM BG/P (Intrepid<sup>3</sup>), and a Cray XT4 (Franklin<sup>4</sup>), and we compare it to various previous classical and Strassen-based algorithms. All our experiments are in double precision on random input matrices. CAPS performs less communication than communication-optimal classical algorithms, and much less than previous Strassen-based algorithms. As a result it outperforms all classical algorithms, both on large problems (because of the lower flop count of Strassen) and on small problems scaled up to many processors (which are communication bound, so the lower communication costs of CAPS make it superior). It also outperforms previous Strassen-based algorithms because of its lower communication costs.

Effective performance is a useful construct for comparing classical and fast matrix multiplication algorithms. It is the performance, normalized with respect to the arithmetic complexity of classical matrix multiplication,  $2n^3$ :

Effective flop/s =

$$\frac{2n^3}{\text{Execution time in seconds}}$$

.

For classical algorithms, this gives exactly the flop rate. For fast matrix multiplication algorithms it gives the relative performance, but does not accurately represent the number of floating point operations performed.

<sup>&</sup>lt;sup>2</sup>For machine details, see http://www.nersc.gov/users/computational-systems/hopper

<sup>&</sup>lt;sup>3</sup>For machine details, see http://www.alcf.anl.gov/intrepid

$<sup>^4</sup>$ For machine details, see http://www.nersc.gov/users/computational-systems/retired-systems/franklin

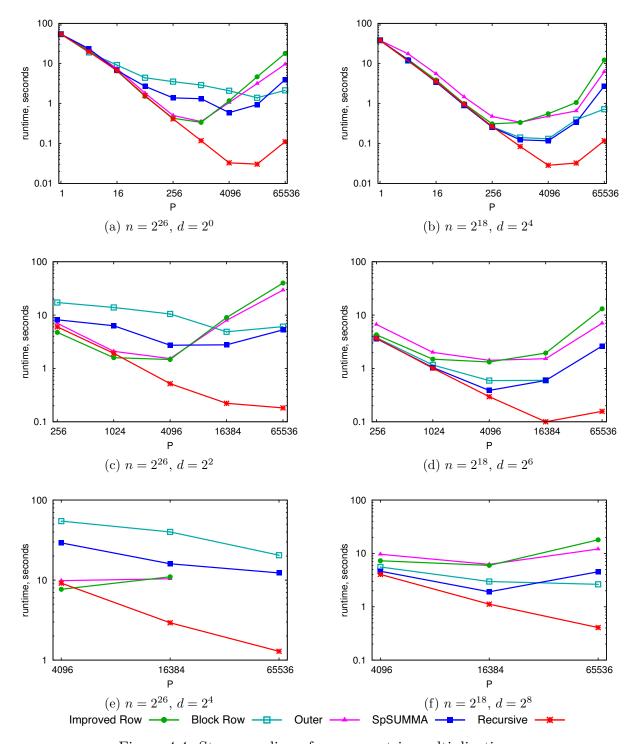

For each of the three machines, we present two types of plots. First, in Figures 2.4a, 2.4c, and 2.4e, we show strong scaling plots for a fixed, large matrix dimension where the x-axis corresponds to number of processor cores (on a log scale) and the y-axis corresponds to fraction of peak performance, as measured by the effective performance. Horizontal lines in the plots correspond to perfect strong scaling.

There are general trends for all algorithms presented in these plots. On the left side of the plots, the number of processors is small enough such that the input and output matrices nearly fill the memories of the processors. As the number of processors increases, both 2.5D and CAPS can exhibit perfect strong scaling within limited ranges. We demarcate the strong-scaling range of CAPS as defined in Section 1.1 with a shaded region. The slightly larger strong-scaling range for the classical 2.5D algorithm is also shown. To the right of the strong scaling range, CAPS must begin to lose performance, as per-processor communication no longer scales with 1/P. While CAPS performance should theoretically degrade more slowly than classical algorithms, network resource contention can also be a limiting factor. The pattern of BFS and DFS steps used by CAPS for these benchmarks is shown in Table 2.2 when the number of MPI processes is a power of 7.

Second, we show execution time for fixed, small matrix dimension over an increasing number of processors. See Figures 2.4b, 2.4d, and 2.4f. For these problem sizes, the execution time is dominated by communication, and the speedup relative to classical algorithms is based primarily on decreases in communication. The optimal number of processors to minimize time to solution varies for each implementation and machine. These plots do not show strong scaling ranges. For both 2.5D and CAPS if a problem fits on one processor, that is  $P_{\min} = 1$ , then for 2.5D  $P_{\max} = P_{\min}^{1.5} = 1$  and for CAPS  $P_{\max} = P_{\min}^{\omega_0/2} = 1$ , which means that there is no strong scaling range.

Note that because several of the implementations, including CAPS, are prototypes, each has its own requirement on the matrix size n and the number of MPI processes P. We have arranged for all algorithms in a given plot to use the same value of n, but the values of P usually do not match between algorithms. In both types of plots, we are comparing CAPS performance with the best classical implementations and previous Strassen-based approaches. To simplify the plots, we omit the performance of algorithms that are dominated by other similar algorithms.

### 2.5.1 Cray XE6 Hopper

Hopper is a Cray XE6 at the National Energy Research Scientific Computing Center. It consists of 6,384 compute nodes, each of which has 2 twelve-core AMD "MagnyCours" 2.1 GHz processors, and 32 GB of DRAM (384 of the nodes have 64 GB of DRAM). The 24 cores are divided between 4 NUMA regions. Parallelism between the 6 cores in a NUMA region comes from the threaded BLAS implementation in Cray's LibSci version 11.0.05. Hopper's peak double precision rate is 50.4 Gflop/s per NUMA region or 1.28 Pflop/s for the entire machine. As of November 2011, it was ranked number 8 on the TOP500 list [53], with a LINPACK score of 1.05 Tflop/s on a matrix of dimension about 4.5 million.

Figure 2.4: Strong scaling results on three machines. Left column: effective performance on large matrices (up is good). Right column: execution time on small matrices (down is good).

| Machine, $n$    | P     | cores | pattern               | memory use per process |

|-----------------|-------|-------|-----------------------|------------------------|

| Hopper, 131712  | 343   | 2058  | D,B,B,B,D,D,D         | 5615 MB                |

| Hopper, 131712  | 2401  | 14406 | B,B,B,B,D,D,D         | 4816 MB                |

| Intrepid, 65856 | 343   | 1372  | $_{\mathrm{D,B,B,B}}$ | 1319 MB                |

| Intrepid, 65856 | 2401  | 9604  | $_{\mathrm{B,B,B,B}}$ | 1119 MB                |

| Intrepid, 65856 | 16807 | 67228 | B,B,B,B,B             | 289 MB                 |

| Franklin, 94080 | 49    | 196   | D,D,B,B,D,D           | 6819 MB                |

| Franklin, 94080 | 343   | 1372  | B,B,D,B,D,D           | 5902 MB                |

| Franklin, 94080 | 2401  | 9604  | B,B,B,B,D,D           | 2449 MB                |

Table 2.2: The pattern of BFS and DFS steps and memory usage for CAPS.

CAPS outperforms all of the previous algorithms. For the large problem (n=131712), it attains performance as high as 30% above the peak for classical matrix multiplication, 83% above 2D, and 75% above Strassen-2D. On this machine, we benchmark ScaLAPACK/PBLAS (part of Cray's LibSci version 11.0.03) as the 2D algorithm. Since we were not able to modify that code, the 2D-Strassen numbers are simulated based on single-node benchmarks of the corresponding local matrix multiplication size. We tested the 2.5D code tuned for Intrepid on Hopper; for large problems it performed worse than ScaLAPACK, and since it was not tuned for Hopper, we do not show results for 2.5D, Strassen-2.5D, or 2.5D-Strassen. We would expect that 2.5D code, properly tuned for Hopper, would outperform 2D. For the small problem (n=4704), we observed speedups of up to 66% over 2.5D, which happened to be the best of the other algorithms for this problem size.

## 2.5.2 IBM BlueGene/P Intrepid

Intrepid is an IBM BG/P at the Argonne Leadership Computing Facility. It consists of 40,960 compute nodes, each of which has a quad-core IBM PowerPC 450 850 MHz processor, and 2 GB of DRAM. Intrepid's peak double precision rate is 13.6 Gflop/s per node, or 557 Tflop/s for the entire machine. We obtain on-node parallelism using the threaded BLAS implementation in IBM's ESSL version 4.4.1-0. As of November 2011, it was ranked number 23 on the TOP500 list [53], with a LINPACK score of 459 Tflop/s. Intrepid allows allocations only in powers of two nodes (with a few exceptions), but in our performance data we count only the nodes we use.

On Intrepid, the most efficient classical code is 2.5D and is well-tuned to the architecture. It consistently outperforms Strassen-2D and Strassen-2.5D, so we omit those algorithms in the performance plots. The 2D and 2.5D code are from [61]. For the large problem (n = 65856), CAPS achieves a speedup of up to 57% over 2.5D or 2.5D-Strassen; for the small problem (n = 4704), the best speedup is 12%.

#### 2.5.3 Cray XT4 Franklin

Franklin is a recently retired Cray XT4 at the National Energy Research Scientific Computing Center. It consists of 9,572 compute nodes, each of which has a quad-core AMD "Budapest" 2.3 GHz processor, and 8 GB of DRAM. Franklin's peak double precision rate is 36.8 Gflop/s per node, or 352 Tflop/s for the entire machine. On each node, we use the threaded BLAS implementation in Cray's LibSci version 10.5.02. As of November 2011, it was ranked number 38 on the TOP500 list [53], with a LINPACK score of 266 Tflop/s on a matrix of dimension about 1.6 million.

CAPS outperforms all of the previous algorithms, and attains performance as high as 33% above the theoretical maximum for classical algorithms, as shown in Figure 2.4e. The largest speedups we observed for the large problem (n=94080) was 103% faster than 2.5D, the fastest classical algorithm, and 187% faster than Strassen-2D, the best previous Strassen-based algorithm. For the small problem size (n=3136), we observed up to 84% improvement over 2.5D, which was the best among the all other approaches. The 2D and 2.5D code are from [61].

For a matrix dimension of n=188160, we observed an aggregate effective performance rate of 351 Tflop/s which exceeds the LINPACK score. Note that for this run CAPS used only 7203 (75%) of the nodes and a matrix of less than one eighth the dimension used for the TOP500 number. In fact, increasing the matrix size to n=263424 increases its effective performance to 388 Tflop/s, higher than Franklin's theoretical peak for classical algorithms.

### 2.5.4 CAPS vs. Strassen-based algorithms

Figure 2.5 compares the performance of CAPS with the previous Strassen-based approaches on Intrepid. The plot shows, for a fixed matrix dimension and number of processors, both the effective and actual performance of the two previous Strassen-based algorithms and CAPS over various numbers of Strassen steps. For a given number of Strassen steps, the three algorithms do (almost) the same number of flops. Note that since the number of nodes is 49, CAPS is defined only for at least 2 Strassen steps.

For this matrix dimension, CAPS attains highest effective performance (shortest time to completion) at 4 Strassen steps. We see that the actual performance for CAPS (and the other two algorithms) decreases with the number of Strassen steps, as it becomes harder to do the fewer flops as efficiently.

In the case of 2D-Strassen, varying the number of Strassen steps means varying how each local matrix multiplication is performed. For the local matrix dimension of n=3136, two Strassen steps is optimal, and the improvement in effective performance is modest because the matrix dimension is fairly small. In the case of Strassen-2D, both effective and actual performance degrade with each Strassen step. This is due to the increasing communication costs of the algorithm, which outweigh the computational savings.

Figure 2.5: Efficiency at various numbers of Strassen steps, n = 21952, on 49 nodes (196 cores) of Intrepid. Effective performance is relative to  $2n^3$  flops and actual performance is relative to the actual number of flops performed.

### 2.6 Performance Model

In this section, we introduce a performance model in order to predict performance on a distributed-memory parallel machine. We include a single-node performance model to more accurately represent local computation. The main goals of the performance model are to validate the theoretical analysis of CAPS to real performance, identify areas which might benefit from further optimization, and make predictions for performance on future hardware.

We choose to validate our model on Intrepid because its performance is very consistent (usually less than 1% variation in execution time, versus 10-20% on Hopper) and also because we believe there is opportunity for topology-aware optimizations, which we discuss in Section 2.6.4.

### 2.6.1 Single Node

Due to the sensitivity of Strassen performance to DGEMM performance and the difficulty of modeling DGEMM performance accurately for small problems, we use a third degree polynomial of best fit to match the measured time of ESSL's implementation of the classical algorithm (DGEMM). Besides making calls to DGEMM, Strassen's algorithm consists of performing matrix additions which are communication bound. Thus, we measured the time of DAXPY per scalar addition, which is fairly independent of matrix size.

Let  $T_{\text{DGEMM}}(n)$  be the polynomial for the time cost of classical matrix multiplication of dimension n and  $T_{\text{DAXPY}}$  be the cost per scalar addition for large vectors. We obtain the single node performance model for the time cost of Strassen's algorithm using s steps of Strassen on a problem of size n as

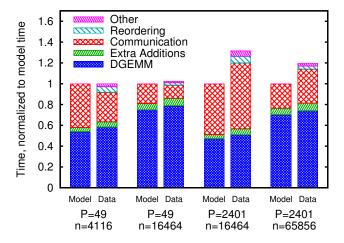

Figure 2.6: Comparison of the sequential model to the actual performance of classical and Strassen matrix multiplication on four cores (one node) of Intrepid.

$$T_{\text{seq}}(n) = \min_{s} \left\{ 7^s \cdot T_{\text{DGEMM}}\left(\frac{n}{2^s}\right) + \sum_{i=0}^{s-1} 9 \cdot T_{\text{D AXPY}} \cdot \left(\frac{7}{4}\right)^i \frac{n^2}{4} \right\} \tag{2.6}$$

The constant 9 comes from the fact that in Strassen-Winograd, for each of A and B, four sub-matrices must be read and four written (since three outputs are copies of inputs), and to compute C, seven input matrices must be read and four written; whereas  $T_{\text{DAXPY}}$  is essentially the time to read two words and write one word. Alternately, one can make 15 calls to DAXPY, one for each matrix addition, which yields a constant of 15 but allows the use of a tuned subroutine. We found better performance using DAXPY on Intrepid, but with enough optimization, an implementation based on the first approach should be more efficient.

The parameters of our single node model (in seconds) are:  $T_{\text{DGEMM}}(n) = 2.04 \cdot 10^{-10} n^3 + 2.14 \cdot 10^{-8} n^2 - 4.18 \cdot 10^{-6} n + 2.11 \cdot 10^{-3}$  and  $T_{\text{DAXPY}} = 3.66 \cdot 10^{-9}$ .

We present actual and modeled performance of both classical and Strassen performance on a single node in Figure 2.6. Note that the classical model is nearly indistinguishable from the data in the plot because it is a curve of best fit. By minimizing over s, the model from Equation (2.6) chooses the optimal cutoff point (around n = 1000) to switch to the classical algorithm, and the performance of Strassen matches the classical algorithm below that point.

In Figure 2.7 we show a breakdown of time between additions and multiplications (calls to DGEMM) for both the model and the actual implementation. For this problem size, the optimal number of Strassen steps is 2, where the time is almost completely dominated by the multiplications. Note that the model predicts better performance for the additions than the implementation achieves, but the main determining factor for optimal number of Strassen steps is the performance of DGEMM for the different problem sizes.

Figure 2.7: Time breakdown comparison between the sequential model and the data for n = 4097. Both model and data times are normalized to the modeled classical algorithm time.

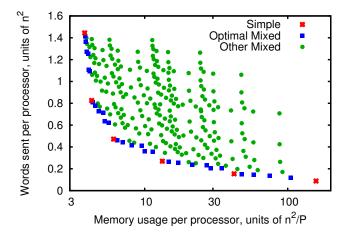

#### 2.6.2 Distributed Machine