# ,Sistemi Digitali P-Z Appello 22 Gennaio 2009

### Esercizio 1 (15 punti)

Seguendo il procedimento visto a lezione, progettare una rete sequenziale, che riceve in ingresso una sequenza x e produce due uscite, z1 e z0, tali che:

z1 produce il bit di parità pari rispetto agli ultimi tre bit . Un bit di parità pari è posto uguale a 1 se il numero di 1 in un certo insieme di bit è dispari (facendo diventare il numero totale di uno, incluso il bit di parità, pari).

z0 produce l'AND tra gli ultimi due bit come illustrato nel seguente esempio:

x: 00110110001111 z1: 00100000101011 z0: 00010010000111

### Esercizio 2 (12 punti)

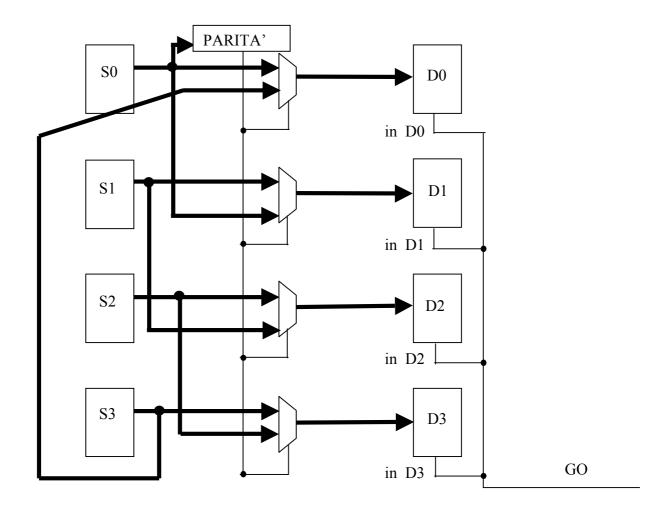

Si hanno quattro registri sorgente S0, S1, S2 e S3 e quattro registri destinazione D0, D1, D2 e D3 di 3 bit ciascuno. Si vuole realizzare un'interconnessione tale che:

- se il numero di 1 memorizzati in S0 è pari allora Di ← Si

- altrimenti  $D_{(i+1) \mod 4} \leftarrow Si$

Si supponga infine di avere un segnale esterno GO che abilita le operazioni descritte se e solo se GO = 1. Si descriva l'interconnessione dettagliando tutti i segnali di controllo e le connessioni richieste.

#### Esercizio 3 (3 punti)

Data la stringa binaria X: 10111 calcolarne il valore in decimale, per i tre seguenti codici di rappresentazione:

X è un intero in complemento a due

X è un numero naturale

X è un numero in virgola fissa con due bit per la parte frazionaria

# Sistemi Digitali P-Z Appello 22 Gennaio 2009

### Compito B

**NOME:**

COGNOME: MATRICOLA:

## Esercizio 1 (12 punti)

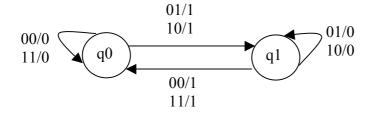

Disegnare l'automa che riceve in ingresso due stringhe x2x1 e produce in uscita 1 se la coppia x2 x1 ricevuta in t differisce dalla precedente (ricevuta in t-1) per un solo bit (altrimenti produce 0) come illustrato nel seguente esempio (da sinistra verso destra):

x2: 01110100 x1: 00011101 z: 01011101

Nell'istante iniziale, z=0.

Disegnare poi il diagramma temporale rispetto alle sequenze di ingresso date nell'esempio.

### Esercizio 2 (12 punti)

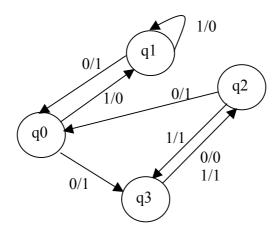

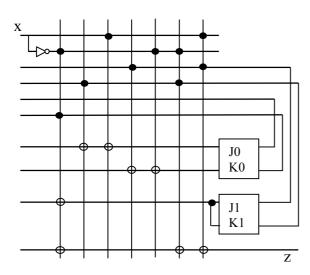

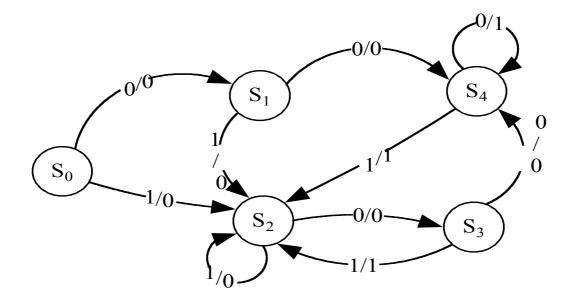

Dato il seguente automa, progettare la rete sequenziale secondo il procedimento di sintesi illustrato a lezione, utilizzando FF di tipo JK e realizzando la parte combinatoria sia con porte logiche che con PLA.

# Esercizio 3 (6 punti)

Dati A=47 e B=12 eseguire la somma e la sottrazione nella rappresentazione in complemento a due.

# Sistemi Digitali P-Z Appello 22 Gennaio 2009

#### Esonero 1

**NOME:**

**COGNOME:**

**MATRICOLA:**

### Esercizio 1 (12 punti)

Progettare una rete sequenziale con 2 linee di ingresso x e y e una linea di uscita z tale che: z = 1 ogni volta che sono state ricevute tre coppie (non consecutive) xy=00, dopodichè l'automa riparte dallo stato iniziale.

Esempio x: **0**1011**00**10111**0**00

y: **0**0101**00**10011010

z: 000000100000001

(leggere le sequenze da sinistra).

# Esercizio 2 (10 punti)

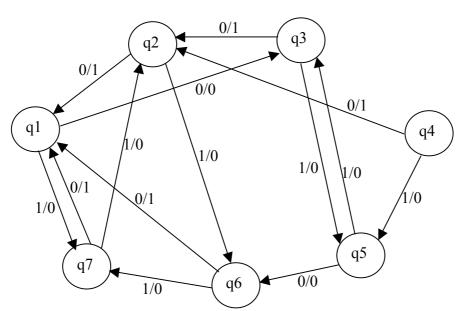

Minimizzare il seguente automa

Rispetto all'automa minimo tracciare il diagramma temporale per la sequenza di ingresso10010100, partendo dallo stato minimo a cui appartiene q1.

# Sistemi Digitali P-Z Appello 22 Gennaio 2009

#### Esonero 2

**NOME:**

COGNOME: MATRICOLA:

**Esercizio 1** (14 punti) Minimizzare l'automa descritto dalla seguente tabella degli stati futuri (A, B, ecc sono i nomi degli stati)

| stato/input | x=0  | x=1  |

|-------------|------|------|

| A           | G/00 | C/01 |

| В           | G/00 | D/01 |

| С           | D/10 | A/11 |

| D           | C/10 | B/11 |

| Е           | G/00 | F/01 |

| F           | F/10 | E/11 |

| G           | A/01 | F/11 |

**Esercizio 2** (16 punti) Progettare un circuito il cui output è 1 quando viene riconosciuta una delle seguenti stringhe: 001, 101 oppure 000. L'output è zero altrimenti.

Il primo bit che viene letto è il bit **più a sinistra**. Le stringhe sono *sovrapponibili*, nel senso chiarito a lezione.

Pur non essendo richiesta l'applicazione di un criterio formale di minimizzazione dell'automa, sarà elemento di valutazione il numero degli stati complessivi utilizzati.

# Soluzioni compito A

### Esercizio 1

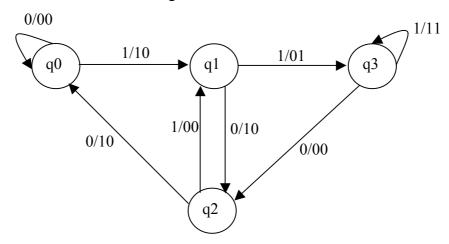

L'automa viene costruito nel seguente modo:

- **gli stati** sono 4 e corrispondono agli ultimi due bit ricevuti, cioè q0 corrisponde a 00, q1 corrisponde a 01, q2 corrisponde a 10 e q3 corrisponde a 11;

- **gli archi** vengono costruiti in modo che, partendo da uno stato e considerato il bit ricevuto in ingresso, si arrivi nello stato che rappresenta gli ultimi due bit ricevuti; ad esempio se si parte dallo stato q1(=01) e si riceve il bit 0 si arriva nello stato q2(=10), mentre se si riceve 1 si arriva nello stato q3(=11);

- i due bit di uscita si calcolano singolarmente secondo la richiesta del testo.

| X | y1 | y0 | <b>Y1</b> | Y0 | z1 | z0 | <b>D1</b> | D0 |

|---|----|----|-----------|----|----|----|-----------|----|

| 0 | 0  | 0  | 0         | 0  | 0  | 0  | 0         | 0  |

| 0 | 0  | 1  | 1         | 0  | 1  | 0  | 1         | 0  |

| 0 | 1  | 0  | 0         | 0  | 1  | 0  | 0         | 0  |

| 0 | 1  | 1  | 1         | 0  | 0  | 0  | 1         | 0  |

| 1 | 0  | 0  | 0         | 1  | 1  | 0  | 0         | 1  |

| 1 | 0  | 1  | 1         | 1  | 0  | 1  | 1         | 1  |

| 1 | 1  | 0  | 0         | 1  | 0  | 0  | 0         | 1  |

| 1 | 1  | 1  | 1         | 1  | 1  | 1  | 1         | 1  |

Osservando la tabella è facile vedere che le espressioni delle funzioni di eccitazione sono:

$$D1 = y0$$

$$D0 = x$$

Utilizziamo le mappe di Karnaugh per minimizzare, se possibile, le espressioni relative alle uscite z1 e z0.

| $x\y1y0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        |    | 1  |    | 1  |

| 1        | 1  |    | 1  | 0  |

$$z1 = \underline{x} \underline{y1} y0 + \underline{x} y1 \underline{y0} + \underline{x} \underline{y1} \underline{y0} + \underline{x} \underline{y1} \underline{y0} + \underline{x} \underline{y1} \underline{y0} = \underline{x} XOR (y1 XOR y0)$$

| $x\y1y0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        |    |    |    |    |

| 1        |    | 1  | 1  |    |

$$z0 = x y0$$

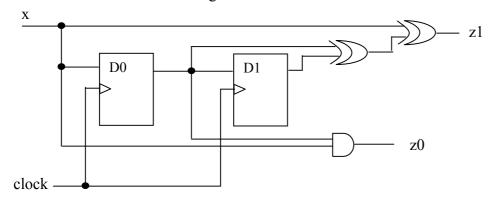

La realizzazione circuitale è la seguente:

# Esercizio 2

Anzitutto realizziamo un circuito combinatorio che calcoli la funzione di parità per un numero di 3 bit (cioè una funzione f(n) che dà 1 se e solo se il numero binario n contiene un numero pari di 1). La tabella è

| X | У | Z | f |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

che è realizzabile col circuito espresso dalla seguente espressione booleana  $x \oplus (y \oplus z)$  (chiamiamo PARITA' tale circuito).

L'interconnessione richiesta è pertanto

#### Esercizio 3

# Soluzioni compito B

## Esercizio 1

L'automa è costituito da due stati:

q0 – stato rappresentato da x2 e x1 uguali

q1 – stato rappresentato da x2 e x1 diversi

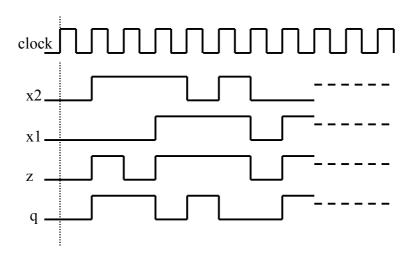

Poiché l'automa è costituito da due stati, basta un bit per la codifica; assegnando agli stati la codifica q0=0 e q1=1, si ottiene il seguente diagramma temporale in cui sono riportati, nell'ordine,

il clock, la sequenza ricevuta su x2, la sequenza ricevuta su x2, la sequenza prodotta su z e la codifica degli stati attraversati a fronte delle sequenze ricevute:

Esercizio 2 L'automa non è minimizzabile. La tabella degli stati futuri è:

| X | y1 | y0 | <b>Y1</b> | Y0 | Z | J1 | K1 | J0 | K0 |

|---|----|----|-----------|----|---|----|----|----|----|

| 0 | 0  | 0  | 1         | 1  | 1 | 1  | X  | 1  | X  |

| 0 | 0  | 1  | 0         | 0  | 1 | 0  | X  | X  | 1  |

| 0 | 1  | 0  | 0         | 0  | 1 | X  | 1  | 0  | X  |

| 0 | 1  | 1  | 1         | 0  | 0 | X  | 0  | X  | 1  |

| 1 | 0  | 0  | 0         | 1  | 0 | 0  | X  | 1  | X  |

| 1 | 0  | 1  | 0         | 1  | 0 | 0  | X  | X  | 0  |

| 1 | 1  | 0  | 1         | 1  | 1 | X  | 0  | 1  | X  |

| 1 | 1  | 1  | 1         | 0  | 1 | X  | 0  | X  | 1  |

Minimizzando con Karnaugh si ottengono le seguenti espressioni:

| $x\y1y0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        | 1  |    | X  | X  |

| 1        |    |    | X  | X  |

$$J1 = \underline{x} \ \underline{y0}$$

| $x\y1y0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        | X  | X  |    | 1  |

| 1        | X  | X  |    |    |

$$K1 = \underline{x} \underline{y0}$$

| $x\y1y0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        | 1  | X  | X  |    |

|          |    |    |    |    |

| 1 | 1 | X | X | 1 |

|---|---|---|---|---|

|   | _ |   |   |   |

$$J0 = \underline{y1} + x$$

| $x\y1y0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        | X  | 1  | 1  | X  |

| 1        | X  |    | 1  | X  |

$$K0 = y1 + \underline{x}$$

| $x\y1y0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        | 1  | 1  |    | 1  |

| 1        |    |    | 1  | 1  |

$$z = \underline{x} \ \underline{y1} + \underline{x} \ \underline{y0} + x \ y1$$

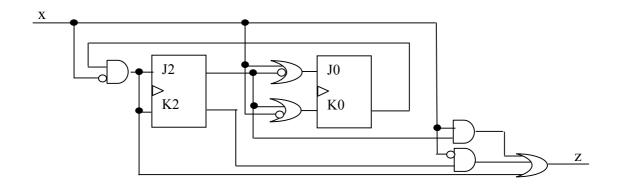

La realizzazione con PLA e con porte logiche sono le seguenti:

#### Esercizio 3

Per rappresentare i valori dati, A e B, nella rappresentazione in complemento a due sono necessari 7 bit; si ha così: A=0101111 e B=0001100, da cui si ricava A+B=0111011.

Per la differenza calcoliamo il valore –B complementando a 1 ogni bit e sommando alla sequenza ottenuta 1; si ha così: -B= 1110100 da cui calcoliamo: A-B=A+(-B)=0100011

N.B. Nella rappresentazione in complemento a 2 i numeri positivi hanno il bit più significativo uguale a zero (infatti per ottenere il valore decimale associato ad una sequenza binaria si assegna la potenza negativa al bit più a sinistra e positiva a tutti gli altri bit).

### Soluzioni Esonero 1

Esonero 1

**NOME:**

**COGNOME:**

**MATRICOLA:**

#### Esercizio 1 (12 punti)

Progettare una rete sequenziale con 2 linee di ingresso x e y e una linea di uscita z tale che: z = 1 ogni volta che sono state ricevute tre coppie (non consecutive) xy=00, dopodichè l'automa riparte dallo stato iniziale.

Esempio x: **0**1011**00**101111**0**00

y: **0**0101**00**1**0**011**0**10 z: 000000100000001

(leggere le sequenze da sinistra).

## Esercizio 2 (10 punti)

Minimizzare il seguente automa

Rispetto all'automa minimo tracciare il diagramma temporale per la sequenza di ingresso10010100, partendo dallo stato minimo a cui appartiene q1.

#### Esercizio 1

L'automa è quello di un contatore mod 3 che cambia stato a fronte della coppia xy=00 e resta nello stato in cui si trova a fronte delle altre tre possibili coppie in ingresso.

Indichiamo i due bit di codifica degli stati w1 e w2 e utilizziamo la seguente codifica:

q0 = 00

q1=01

q2 = 10

La tavola di verità è la seguente :

| xyw1w2 W1W2 z j1k1 j2k | <u>ر</u> |

|------------------------|----------|

|                        |          |

| 0000 01 0 0x x         | )        |

| 0001 10 0 1x 0x        | K        |

| 0010 00 1 x1 x         | )        |

| 0011 xx x x xx x       | K        |

| 0100 00 0 0x x         | )        |

| 0101 01 0 0x 0x        | K        |

| 0110 10 0 x0 x         | )        |

| 0111 xx x x xx x       | K        |

| 1000 00 0 0x x         | )        |

| 1001 01 0 0x 0x        | Κ        |

| 1010 10 0 x0 x         | )        |

| 1011 | XX | X | XX | XX |

|------|----|---|----|----|

| 1100 | 00 | 0 | 0x | x0 |

| 1101 | 01 | 0 | 0x | 0x |

| 1110 | 10 | 0 | x0 | x0 |

| 1111 | XX | X | XX | XX |

Dalla tabella si ricava subito che:

$$j2 = k2 = 0$$

e minimizzando con Karnaugh si ottengono le espressioni:

$$j1 = \underline{x} \underline{y} w2$$

$$k1 = \underline{x} \underline{y}$$

$$z = \underline{x} \underline{y} w1$$

Lo schema circuitale si ottiene facilmente utilizzando le espressioni ricavate.

Le espressioni con FF di tipo D, ottenute minimizzando con le mappe di Karnaugh, sono:

$$d1 = \underline{x} \underline{y} w2 + y w1 + x w1$$

$$d2 = \underline{x} \underline{y} \underline{w1} \underline{w2} + y \underline{w2} + x \underline{w2}$$

#### Esercizio 2

$$A=(1)$$

$$B=(2,6,7)$$

$$C=(3,4)$$

# Soluzioni Esonero 2

#### Esonero 2

**NOME:**

COGNOME: MATRICOLA:

**Esercizio 1** (14 punti) Minimizzare l'automa descritto dalla seguente tabella degli stati futuri (A, B, ecc sono i nomi degli stati)

| stato/input | x=0  | x=1  |

|-------------|------|------|

| A           | G/00 | C/01 |

| В           | G/00 | D/01 |

| С           | D/10 | A/11 |

| D           | C/10 | B/11 |

| Е           | G/00 | F/01 |

| F           | F/10 | E/11 |

| G           | A/01 | F/11 |

**Esercizio 2** (16 punti) Progettare un circuito il cui output è 1 quando viene riconosciuta una delle seguenti stringhe: 001, 101 oppure 000. L'output è zero altrimenti.

Il primo bit che viene letto è il bit **più a sinistra**. Le stringhe sono *sovrapponibili*, nel senso chiarito a lezione.

Pur non essendo richiesta l'applicazione di un criterio formale di minimizzazione dell'automa, sarà elemento di valutazione il numero degli stati complessivi utilizzati.

### Esercizio 1

|   | C,D |     |     |         |   |   |

|---|-----|-----|-----|---------|---|---|

| В |     |     |     |         |   |   |

| C | X   | X   |     | _       |   |   |

| D | X   | X   | A,B |         | _ |   |

| E | C,F | D,F | X   | X       |   | _ |

| F | X   | X   | A,E | B,E C,F | X |   |

|   |     |     | D,F |         |   |   |

| G | X   | X   | X   | X       | X | X |

|   | A   | В   | C   | D       | E | F |

### classi di equivalenza

A'=A,B,E C'=C,D,F G'=G

|    | x=0   | x=1   |

|----|-------|-------|

| A' | G'/00 | C'/01 |

| C' | C'/10 | A'/11 |

| G' | A'/01 | C'/11 |

# Esercizio 2

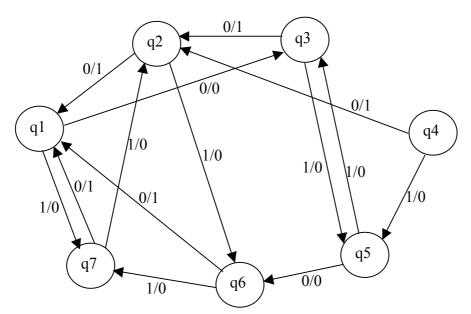

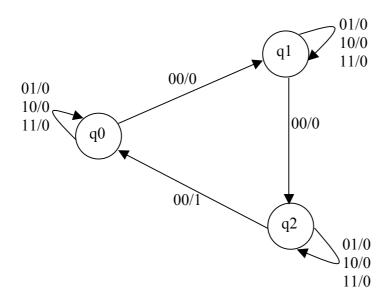

L'automa di Mealy è il seguente:

dove:

- S<sub>0</sub> indica lo stato iniziale

- S<sub>1</sub> lo stato in cui è stato riconosciuto "0"

- S<sub>4</sub> lo stato in cui è stata riconosciuta una stringa "00...0" di lunghezza almeno 2

- S<sub>2</sub> lo stato in cui è stato riconosciuto un "1"

- S<sub>3</sub> lo stato in cui è stato riconosciuto "10"

Si noti che non è necessario tenere uno stato per la stringa "101" perché è sufficiente tenere traccia dell'ultimo "1". Infatti concatenando un bit alla stringa "101" non si ottiene nessuna sequenza valida. Lo stesso ragionamento si può applicare alla stringa "001" e così via. Si poteva anche realizzare l'automa con tutti i possibili stati e poi minimizzarlo, ma sarebbe stato più laborioso.

| Stato | Input 0           | Input 1   |

|-------|-------------------|-----------|

| $S_0$ | $S_{1}/0$         | $S_{2}/0$ |

| $S_1$ | S <sub>4</sub> /0 | $S_{2}/0$ |

| $S_2$ | $S_{3}/0$         | $S_{2}/0$ |

| $S_3$ | S <sub>4</sub> /0 | $S_2/1$ |

|-------|-------------------|---------|

| $S_4$ | $S_4/1$           | $S_2/1$ |

Gli stati si codificano con 3 FF di tipo JK. La tabella degli stati futuri è la seguente:

| Stato          | Q <sub>2</sub> (t) | Q <sub>1</sub> (t) | Q <sub>0</sub> (t) | X | $J_2$ | K <sub>2</sub> | $J_1$ | $K_1$ | $J_0$ | K <sub>0</sub> | $Q_2(t+1)$ | $Q_1(t+1)$ | $Q_0(t+1)$ | Z |

|----------------|--------------------|--------------------|--------------------|---|-------|----------------|-------|-------|-------|----------------|------------|------------|------------|---|

| C              | 0                  | 0                  | 0                  | 0 | 0     | X              | 0     | X     | 1     | X              | 0          | 0          | 1          | 0 |

| $S_0$          | 0                  | 0                  | 0                  | 1 | 0     | X              | 1     | X     | 0     | X              | 0          | 1          | 0          | 0 |

| C              | 0                  | 0                  | 1                  | 0 | 1     | X              | 0     | X     | X     | 1              | 1          | 0          | 0          | 0 |

| $S_1$          | 0                  | 0                  | 1                  | 1 | 0     | X              | 1     | X     | X     | 1              | 0          | 1          | 0          | 0 |

| $S_2$          | 0                  | 1                  | 0                  | 0 | 0     | X              | X     | 0     | 1     | X              | 0          | 1          | 1          | 0 |

| $\mathbf{S}_2$ | 0                  | 1                  | 0                  | 1 | 0     | X              | X     | 0     | 0     | X              | 0          | 1          | 0          | 0 |

| $S_3$          | 0                  | 1                  | 1                  | 0 | 1     | X              | X     | 1     | X     | 1              | 1          | 0          | 0          | 0 |

| 33             | 0                  | 1                  | 1                  | 1 | 0     | X              | X     | 0     | X     | 1              | 0          | 1          | 0          | 1 |

| C              | 1                  | 0                  | 0                  | 0 | X     | 0              | 0     | X     | 0     | X              | 1          | 0          | 0          | 1 |

| $S_4$          | 1                  | 0                  | 0                  | 1 | X     | 1              | 1     | X     | 0     | X              | 0          | 1          | 0          | 1 |

|                | 1                  | 0                  | 1                  | 0 | X     | X              | X     | X     | X     | X              | X          | X          | X          | X |

|                | 1                  | 0                  | 1                  | 1 | X     | X              | X     | X     | X     | X              | X          | X          | X          | X |

|                | 1                  | 1                  | 0                  | 0 | X     | X              | X     | X     | X     | X              | X          | X          | X          | X |

|                | 1                  | 1                  | 0                  | 1 | X     | X              | X     | X     | X     | X              | X          | X          | X          | X |

|                | 1                  | 1                  | 1                  | 0 | X     | X              | X     | X     | X     | X              | X          | X          | X          | X |

|                | 1                  | 1                  | 1                  | 1 | X     | X              | X     | X     | X     | X              | X          | X          | X          | X |

Applicando le mappe di Karnaugh si ottiene:

$$J_1 = x \; , \; K_1 = J_2 = Q_0 \cdot \overset{-}{x} \; , \; K_2 = x \; , \; J_0 = \overline{Q_2 x} \; , \; K_0 = 1 \; , \; z = Q_2 + Q_1 \cdot Q_0 \cdot x$$