#### **COMPITO A**

## Esercizio 1 (13 punti)

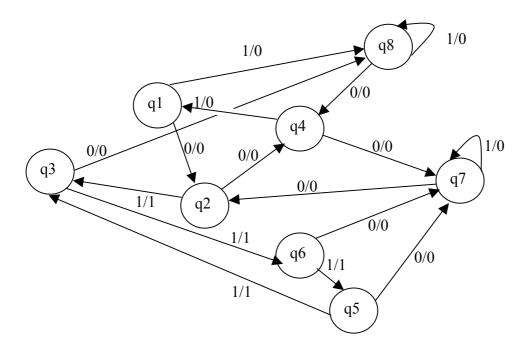

Dato il seguente automa:

- minimizzare l'automa usando la tabella triangolare

- disegnare l'automa minimo

- progettare la rete sequenziale relativa all'automa minimo, secondo il procedimento di sintesi illustrato a lezione, utilizzando FF di tipo JK

- disegnare il diagramma temporale per la sequenza di ingresso 01110011.

## Esercizio 2 (11 punti)

Disegnare l'automa che riceve in ingresso x2 e x1 e produce in uscita  $\mathbf{0}$  se il numero di zero ricevuti su x2 e x1 è pari (altrimenti produce  $\mathbf{1}$ ) come illustrato nel seguente esempio:

x2: 01110100 x1: 00011101 z: 01001110

Disegnare poi il diagramma temporale rispetto alle sequenze di ingresso date nell'esempio.

### Esercizio 3 (6 punti)

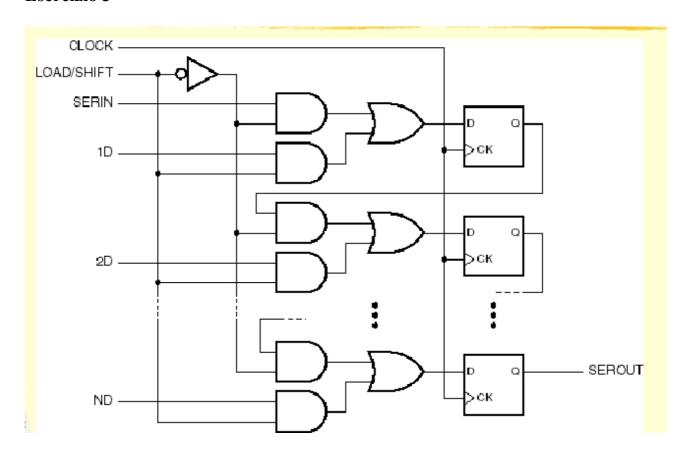

Disegnare il funzionamento di un registro a caricamento parallelo e scaricamento seriale con 3 FF di tipo D.

#### **COMPITO B**

## Esercizio 1 (9 punti)

Data l'espressione booleana (dove le variabili negate sono sottolineate)  $x3 \times 2 \times 1 + x2 \times 1 + x3 \times 1 + x3 \times 2$

- scrivere l'espressione nella forma canonica SOP e nella forma canonica POS,

- minimizzare l'espressione usando la mappa di Karnaugh,

- disegnare il circuito con sole porte NAND.

### Esercizio 2 (16 punti)

Seguendo il procedimento visto a lezione, progettare una rete sequenziale che riceve in ingresso una sequenza x e produce in uscita la somma binaria degli ultimi tre bit ricevuti (su due uscite, z1 e z0) come illustrato nel seguente esempio:

x: 00110110001111 z1: 00011111000111 z0: 00100000101011

Disegnare poi il diagramma temporale rispetto alla sequenza di ingresso data nell'esempio.

## Esercizio 3 (5 punti)

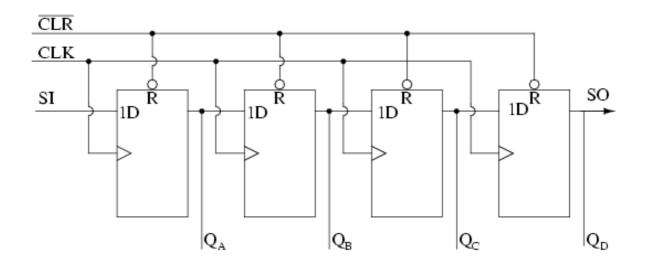

Disegnare il funzionamento di un registro a caricamento seriale e scaricamento parallelo con 4 FF di tipo D.

## **COMPITO A Soluzione esercizio 1**

#### L'automa in forma tabellare è:

|    | 0    | 1    |

|----|------|------|

| Q1 | Q2/0 | Q8/0 |

| Q2 | Q4/0 | Q3/1 |

| Q3 | Q8/0 | Q6/1 |

| Q4 | Q7/0 | Q1/0 |

| Q5 | Q7/0 | Q3/1 |

| Q6 | Q7/0 | Q5/1 |

| Q7 | Q2/0 | Q7/0 |

| Q8 | Q4/0 | Q8/0 |

## La tabella triangolare è:

| Q2 | X          |            | _          |            |       |    |       |

|----|------------|------------|------------|------------|-------|----|-------|

| Q3 | X          | (3,6)(4,8) |            | _          |       |    |       |

| Q4 | (2,7)(1,8) | X          | X          |            | _     |    |       |

| Q5 | X          | (4,7)      | (7,8)(3,6) | X          |       | _  |       |

| Q6 | X          | (4,7)(3,5) | (7,8)(5,6) | X          | (3,5) |    |       |

| Q7 | (7,8)      | X          | X          | (1,7)(2,7) | X     | X  |       |

| Q8 | (2,4)      | X          | X          | (1,8)(4,7) | X     | X  | (2,4) |

|    | Q1         | Q2         | Q3         | Q4         | Q5    | Q6 | Q7    |

Dopo una seconda analisi della tabella triangolare si vede che non ci sono stati equivalenti.

Assegnando la seguente codifica agli stati:

Q1=000

Q2=001

Q3=010

Q4=011

Q5=100

Q6=101

Q7=110

Q8=111

### si ottiene la tabella di verità:

| X | <b>y2</b> | y1 | y0 | <b>Y2</b> | <b>Y1</b> | Y0 | Z | J2K2 | J1K1 | J0K0 |

|---|-----------|----|----|-----------|-----------|----|---|------|------|------|

| 0 | 0         | 0  | 0  | 0         | 0         | 1  | 0 | 0x   | 0x   | 1x   |

| 0 | 0         | 0  | 1  | 0         | 1         | 1  | 0 | 0x   | 1x   | x0   |

| 0 | 0         | 1  | 0  | 1         | 1         | 1  | 0 | 1x   | x0   | 1x   |

| 0 | 0         | 1  | 1  | 1         | 1         | 0  | 0 | 1x   | x0   | x1   |

| 0 | 1         | 0  | 0  | 1         | 1         | 0  | 0 | x0   | 1x   | 0x   |

| 0 | 1         | 0  | 1  | 1         | 1         | 0  | 0 | x0   | 1x   | x1   |

| 0 | 1         | 1  | 0  | 0         | 0         | 1  | 0 | x1   | x1   | 1x   |

| 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | x1 | x0 | x0 |

|---|---|---|---|---|---|---|---|----|----|----|

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1x | 1x | 1x |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0x | 1x | x1 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1x | x1 | 1x |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0x | x1 | x1 |

| 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | x1 | 1x | 0x |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | x0 | 0x | x1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | x0 | x0 | 0x |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | x0 | x0 | x0 |

Le espressioni booleane per le funzioni di eccitazione e per la funzione di uscita z sono (per la complementazione uso la sottolineatura):

$$z = x \underline{y1} y0 + x \underline{y2} \underline{y1} + x \underline{y2} \underline{y1} \underline{y0}$$

$$J2 = \underline{x} y1 + x \underline{y1} \underline{y0}$$

$$K2 = \underline{x} y1 + x \underline{y1} \underline{y0}$$

$$J1 = \underline{x} y2 + x \underline{y0} + \underline{y2} \underline{y0}$$

$$K1 = x \underline{y2} + \underline{x} \underline{y2} \underline{y0}$$

$$J0 = \underline{x} \underline{y2} + x \underline{y2} + \underline{x} \underline{y1}$$

$$K0 = \underline{y2} \underline{y1} + x \underline{y2} + \underline{x} \underline{y2} \underline{y1}$$

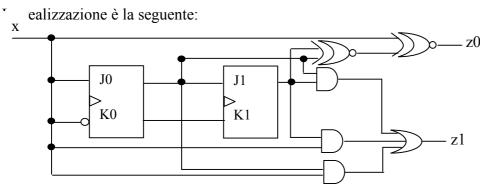

Ottenute le espressioni per le funzioni di minimizzazione è facile disegnare il circuito.

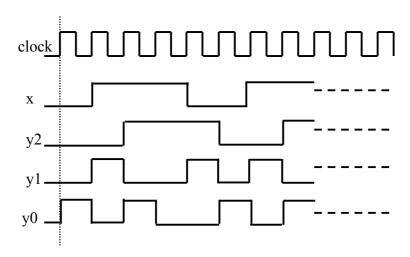

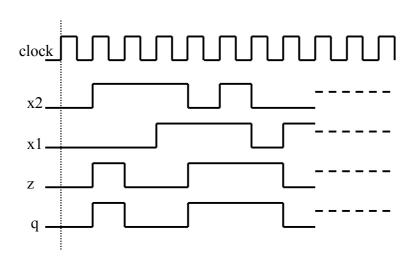

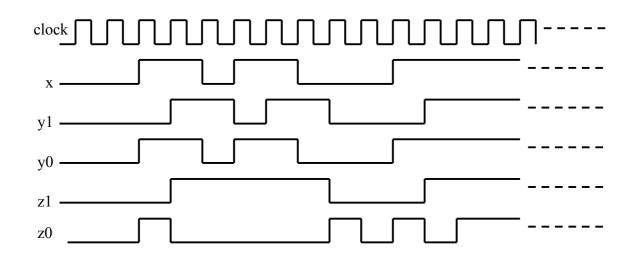

Il diagramma temporale è:

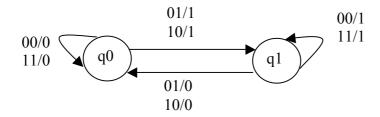

### Esercizio 2

L'automa è costituito da due stati:

q0 – stato in cui si sono ricevuti un numero pari di zero sulle linee x2 e x1

q1 – stato in cui si sono ricevuti un numero dispari di zero sulle linee x2 e x1

Poiché l'automa è costituito da due stati, basta un bit per la codifica; assegnando agli stati la codifica q0=0 e q1=1, si ottiene il seguente diagramma temporale in cui sono riportati, nell'ordine, il clock, la sequenza ricevuta su x2, la sequenza ricevuta su x1, la sequenza prodotta su z e la codifica degli stati attraversati a fronte delle sequenze ricevute:

### Esercizio 3

## Soluzioni compito B

#### Esercizio 1

L'espressione canonica SOP si ottiene nel modo seguente:

```

x3 \ \underline{x2} \ \underline{x1} + \underline{x2} \ x1 + \underline{x3} \ x1 + x3 \ \underline{x2} =  se manca il letterale x_i si moltiplica per (x_i + \underline{x_i}) = 1 = x3 \ \underline{x2} \ \underline{x1} + \underline{x2} \ x1 \ (x3 + \underline{x3}) + \underline{x3} \ x1 \ (x2 + \underline{x2}) + x3 \ \underline{x2} \ (x1 + \underline{x1}) =  = x3 \ \underline{x2} \ \underline{x1} + x3 \ \underline{x2} \ x1 + \underline{x3} \ \underline{x2} \ x1 + \underline{x3} \ \underline{x2} \ x1 + \underline{x3} \ \underline{x2} \ x1 + x3 \ \underline{x2} \ x1 + x3 \ \underline{x2} \ x1 =  eliminando i termini ripetuti = x3 \ \underline{x2} \ \underline{x1} + x3 \ \underline{x2} \ x1 + \underline{x3} \ \underline{x3}

```

L'espressione SOP in forma canonica si può scrivere come OR di mintermini, nel nostro caso è: OR(m1, m3, m4, m5)

L'espressione POS in forma canonica si può scrivere come AND di maxtermini, nel nostro caso è: AND(M0, M2, M6, M7) = (x3 + x2 + x1)(x3 + x2 + x1)(x3 + x2 + x1)(x3 + x2 + x1)

La tabella della funzione è:

| x3               | x2 | x1 | y |

|------------------|----|----|---|

| 0                | 0  | 0  | 0 |

| 0                | 0  | 1  | 1 |

| 0                | 1  | 0  | 0 |

| 0<br>0<br>0<br>0 | 1  | 1  | 1 |

| 1                | 0  | 0  | 1 |

| 1                | 0  | 1  | 1 |

| 1                | 1  | 0  | 0 |

| 1                | 1  | 1  | 0 |

La relativa mappa di Karnaugh

| $\ \ x2x1$ | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| x3\        |    |    |    |    |

| 0          | 0  | 1  | 1  | 0  |

| 1          | 1  | 1  | 0  | 0  |

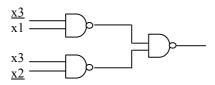

Dalla mappa di Karnaugh si ottiene la forma minimale SOP:  $\underline{x3} \times 1 + x3 \times 2$ .

La realizzazione con sole porte NAND di un'espressione della forma AND-to-OR come la minimale SOP scritta, si ottiene sostituendo porte NAND alle porte AND e alla porta OR.

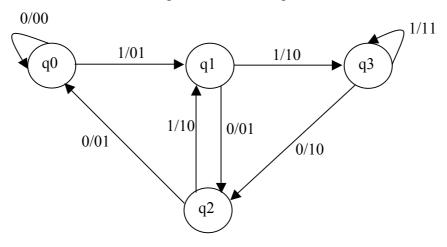

#### Esercizio 2

L'automa viene costruito nel seguente modo:

- **gli stati** sono 4 e corrispondono agli ultimi due bit ricevuti, cioè q0 corrisponde a 00, q1 corrisponde a 01, q2 corrisponde a 10 e q3 corrisponde a 11;

- **gli archi** vengono costruiti in modo che, partendo da uno stato e considerato il bit ricevuto in ingresso, si arrivi nello stato rappresenti correttamente gli ultimi due bit ricevuti; ad esempio se si parte dallo stato q1(=01) e si riceve il bit 0 si arriva nello stato q2(=10), mentre se si riceve 1 si arriva nello stato q3(=11);

- **i due bit di uscita** si calcolano sommando i due bit che rappresentano lo stato e il bit che si riceve in ingresso; ad esempio se si parte dallo stato 01 e si riceve il bit 0 si produce come output 01, mentre se si riceve 1 si produce come output 10.

| X | y1 | y0 | <b>Y1</b> | Y0 | z1 | z0 | J1 | K1 | J0 | K0 |

|---|----|----|-----------|----|----|----|----|----|----|----|

| 0 | 0  | 0  | 0         | 0  | 0  | 0  | 0  | X  | 0  | X  |

| 0 | 0  | 1  | 1         | 0  | 0  | 1  | 1  | X  | X  | 1  |

| 0 | 1  | 0  | 0         | 0  | 0  | 1  | X  | 1  | 0  | X  |

| 0 | 1  | 1  | 1         | 0  | 1  | 0  | X  | 0  | X  | 1  |

| 1 | 0  | 0  | 0         | 1  | 0  | 1  | 0  | X  | 1  | X  |

| 1 | 0  | 1  | 1         | 1  | 1  | 0  | 1  | X  | X  | 0  |

| 1 | 1  | 0  | 0         | 1  | 1  | 0  | X  | 1  | 1  | X  |

| 1 | 1  | 1  | 1         | 1  | 1  | 1  | X  | 0  | X  | 0  |

Minimizzando con Karnaugh si ottengono le seguenti espressioni:

| $x\y1y0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        |    | 1  | X  | X  |

|          |    |    |    |    |

$$J1 = y0$$

| $x\y1y0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        | X  | X  |    | 1  |

| 1 _      | X  | X  |    | 1  |

$$K1 = \underline{y0}$$

| $x\y1y0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        |    | X  | X  |    |

| 1        | 1  | X  | X  | _1 |

$$J0 = x$$

| x\y1y0 | 00 | 01 | 11 | 10 |

|--------|----|----|----|----|

| 0      | X  | 1  | 1  | X  |

| 1      | X  |    |    | X  |

$$K0 = \underline{x}$$

| $x\y1y0$ | 00 | 01 | <u>11</u> | 10 |

|----------|----|----|-----------|----|

| 0        |    |    | 1         |    |

| 1        |    | 1  | 1         | 1  |

$$z1 = y1 y0 + x y0 + x y1$$

| $x\y1y0$ | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        |    | 1  |    | 1  |

| 1        | 1  |    | 1  |    |

$$z0 = \underline{x} \ \underline{y1} \ y0 + \underline{x} \ y1 \ \underline{y0} + x \ \underline{y1} \ \underline{y0} + x \ y1 \ y0 = x \oplus (y1 \oplus y2)$$

Il diagramma temporale è:

# Esercizio 3