Per venir elaborate o memorizzate, le informazioni devono essere trasferite da un registro all'altro all'interno di un elaboratore.

Il trasferimento di informazioni tra registri viene realizzato tramite **reti di interconnessione.**

N.B.: Se i registri sono a scaricamento parallelo (PIPO/SIPO), l'informazione in realtà viene *copiata* dal registro sorgente a quello destinazione.

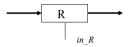

Non ci interessa la modalità di caricamento/scaricamento; assumiamo che un registro è

dove le linee spesse denotano *n* bit (se il registro è formato da *n* FF) e la linea *in R* abilita il registro alla scrittura (come la linea *load* per il PIPO)

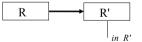

# Sorgente e destinazione prefissata: porte logiche

Per trasferire il contenuto di R in R', basta collegare l'output di R all'input di R' e settare *in R'* ogni volta che si vuole effettuare il trasferimento:

Ciò in realtà rappresenta in maniera schematica la seguente interconnessione, assumendo che i registri siano sequenze di FF di tipo SR:

#### Sorgente e destinazione prefissata: Buffer tri-states

Il buffer tri-states è un interruttore elettronico, schematicamente rappresentato come

che può assumere tre stati (da cui il nome):

- circuito aperto: s = 0;

- circuito chiuso e uscita 0: se s=1 e a=0;

- circuito chiuso e uscita 1: se s=1 e a=1.

Invece che usare porte AND, nella realizzazione precedente possiamo usare buffer tri-states con segnale di controllo il bit  $in_R'$ :

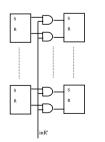

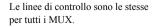

## Interconnessione tramite MUX: dettaglio (a linee singole)

Nella rappresentazione precedente, le frecce marcate rappresentano *n* linee; quindi, anche i MUX sono in realtà *n*!!

- Il primo FF di ogni registro sorgente è connesso con il primo MUX, la cui uscita va al primo FF di R<sub>4</sub>;

- il secondo FF di ogni registro sorgente è connesso con il secondo MUX, la cui uscita va al secondo FF di R<sub>d</sub>;

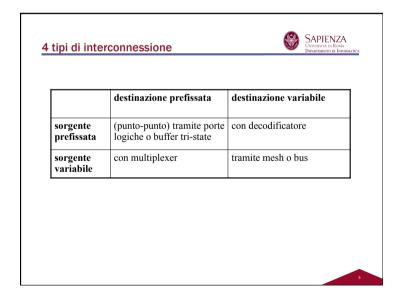

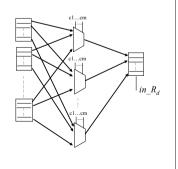

### Sorgente variabile e destinazione prefissata: interconnessione con multiplexer

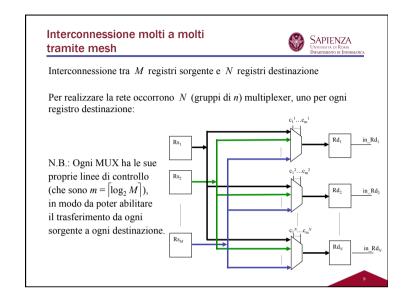

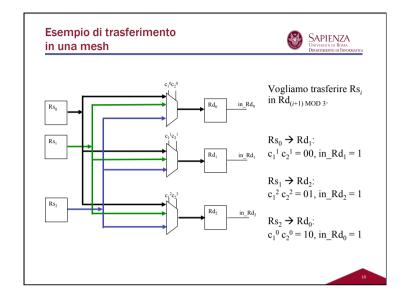

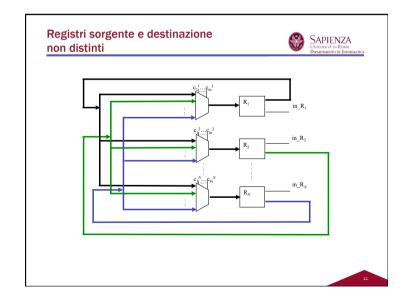

Il registro sorgente può essere un qualsiasi registro  $R_i$  di un insieme di N registri, mentre il registro destinazione  $R_d$  è fissato.

Questo può essere fatto usando un MUX le cui entrate sono gli output degli *N* registri sorgente e la cui uscita viene data in ingresso al registro destinazione:

I segnali di selezione del multiplexer  $c_1, ... c_m$  sono  $m = \lceil \log_2 N \rceil$  e forniscono la codifica binaria dell'indice i del registro  $R_i$  il cui contenuto deve essere copiato in  $R_d$ .

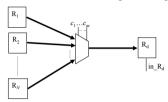

### Sorgente prefissata e destinazione variabile: interconnessione con decodificatore

Il registro sorgente  $R_s$  è fissato, mentre il registro destinazione può essere un qualsiasi registro  $R_s$  di un insieme di N registri.

Questo può essere fatto mandando in input a ogni registro destinazione l'output del registro sorgente e usando un decodificatore per abilitare la scrittura sul registro destinazione desiderato:

Gli ingressi del decodificatore  $c_1, ..., c_m$  sono  $m = \lceil \log_2 N \rceil$  e forniscono la codifica binaria dell'indice i del registro  $R_i$  dove copiare l'informazione contenuta in  $R_s$ .

Le uscite del decodificatore vengono messe in AND con un segnale "globale" di scrittura  $(in\_R')$  e forniscono i segnali  $in\_R_i$  per i registri destinazione.

#### 2 tipi di memoria:

- centrale (nel microprocessore): poche decine di registri veloci

- di massa: milioni di registri realizzati con tecnologia più economica

#### 2 tipi di interconnessione:

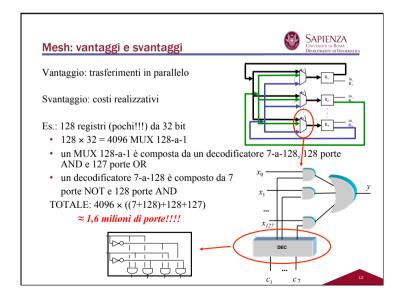

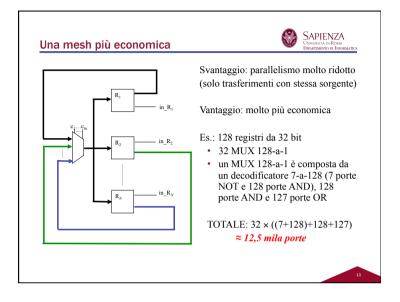

- mesh tra i registri del microprocessore

- bus per trasferire informazioni dalla memoria di massa a quella centrale

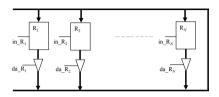

### Interconnessione molti-a-molti tramite bus

Riducendo il parallelismo, si può realizzare l'interconnessione di prima in maniera ancora più economica tramite un *bus*, cioè un fascio di *n* linee che interconnettono tutti i registri, sia in entrata che in uscita.

N.B.: per evitare conflitti nell'uso del bus, ogni uscita è controllata da un (insieme di n) buffer tri-states, ognuno regolato dal segnale di controllo  $da_R^i$ , che vale 1 se il registro sorgente è  $R_i$ . Ovviamente, bisognerà garantire che al più uno di tali segnali valga "1" ad ogni istante.

Es. (128 registri da 32 bit):  $128 \times 32 \approx 4100$  buffer tri-states

## Progettare una rete di interconnessione

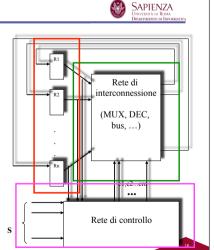

Si distinguono 3 parti:

- i registri coinvolti (R<sub>1</sub>...R<sub>N</sub>)

- la rete di interconnessione che, nel caso più generale, consente di trasferire il contenuto di ogni registro in ogni altro registro

- la rete combinatoria di controllo che analizza alcune condizioni interne (contenuto dei registri) o esterne (segnali S) e genera gli opportuni comandi per i circuiti che costituiscono la rete di interconnessione