# Appello di Progettazione di Sistemi Digitali 2 Luglio 2013 - Docenti: Proff. Gorla e Massini

**Esercizio 1 (5 punti):** Analizzare il seguente circuito sequenziale fino alla descrizione verbale del circuito, assumendo che all'inizio i flip flop siano impostati a  $q2 \ q1 \ q0 = 110$ .

#### SOLUZIONE:

Le espressioni booleana associate alle entrate dei FF e all'uscita del circuito sono:

$$T0 = x$$

$$J1 = x Q2$$

$$K1 = Q2$$

$$D2 = Q0 Q1$$

$$z = x Q2$$

Da esse si può costruire la tabella degli stati futuri

| x | $\overline{Q2}$ | Q1 | Qθ | <i>T0</i> | <i>J1</i> | <i>K1</i> | <b>D</b> 2 | <i>Q2</i> ' | <u>Q</u> 1' | Qθ' | z |

|---|-----------------|----|----|-----------|-----------|-----------|------------|-------------|-------------|-----|---|

| 0 | 0               | 0  | 0  | 0         | 0         | 0         | 0          | 0           | 0           | 0   | 0 |

| 0 | 0               | 0  | 1  | 0         | 0         | 0         | 0          | 0           | 0           | 1   | 0 |

| 0 | 0               | 1  | 0  | 0         | 0         | 0         | 0          | 0           | 1           | 0   | 0 |

| 0 | 0               | 1  | 1  | 0         | 0         | 0         | 1          | 1           | 1           | 1   | 0 |

| 0 | 1               | 0  | 0  | 0         | 0         | 1         | 0          | 0           | 0           | 0   | 0 |

| 0 | 1               | 0  | 1  | 0         | 0         | 1         | 0          | 0           | 0           | 1   | 0 |

| 0 | 1               | 1  | 0  | 0         | 0         | 1         | 0          | 0           | 0           | 0   | 0 |

| 0 | 1               | 1  | 1  | 0         | 0         | 1         | 1          | 1           | 0           | 1   | 0 |

| 1 | 0               | 0  | 0  | 1         | 0         | 0         | 0          | 0           | 0           | 1   | 0 |

| 1 | 0               | 0  | 1  | 1         | 0         | 0         | 0          | 0           | 0           | 0   | 0 |

| 1 | 0               | 1  | 0  | 1         | 0         | 0         | 0          | 0           | 1           | 1   | 0 |

| 1 | 0               | 1  | 1  | 1         | 0         | 0         | 1          | 1           | 1           | 0   | 0 |

| 1 | 1               | 0  | 0  | 1         | 1         | 1         | 0          | 0           | 1           | 1   | 1 |

| 1 | 1               | 0  | 1  | 1         | 1         | 1         | 0          | 0           | 1           | 0   | 1 |

| 1 | 1               | 1  | 0  | 1         | 1         | 1         | 0          | 0           | 0           | 1   | 1 |

| 1 | 1               | 1  | 1  | 1         | 1         | 1         | 1          | 1           | 0           | 0   | 1 |

Prendendo come configurazione iniziale quella per cui Q2 Q1 Q0 = 110, si ottiene il seguente automa che descrive il funzionamento del circuito (N.B.: alcuni stati sono irraggiungibili partendo da 110, pertanto sono omessi nell'automa):

|     | 0     | 1     |

|-----|-------|-------|

| 110 | 000/0 | 001/1 |

| 000 | 000/0 | 001/0 |

| 001 | 001/0 | 000/0 |

Si può notare che l'automa non è minimo, e fondere gli stati 000 e 001, ottenendo

|    | 0    | 1    |

|----|------|------|

| SO | S1/0 | S1/1 |

| S1 | S1/0 | S1/0 |

Cioè, questo circuito da 1 solo quando riceve in ingresso sequenze di bit del tipo 1000...000...

# Esercizio 2 (12 punti)

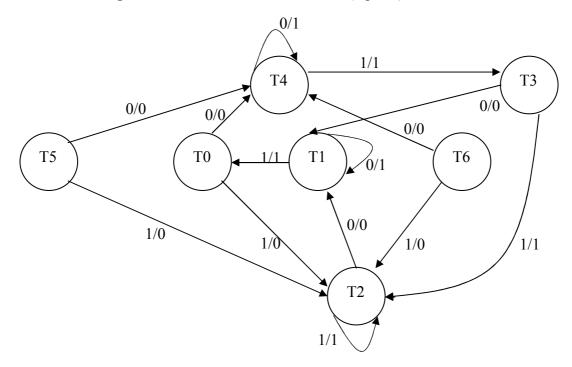

a) Minimizzare il seguente automa con stato iniziale T0 (4 punti):

#### SOLUZIONE:

Si può osservare che da T0 gli stati T5 e T6 non sono raggiungibili e quindi rimuoverli subito. All'automa così ottenuto si applica l'algoritmo di minimizzazione (richiesto in sede d'esame, qui omesso per brevità), ottenendo che gli stati T2 e T3 sono equivalenti, da cui l'automa minimo è

|                   | 0    | 1    |

|-------------------|------|------|

| <b>S0</b> (T0)    | S3/0 | S2/0 |

| <b>S1</b> (T1)    | S1/1 | S0/1 |

| <b>S2</b> (T2+T3) | S1/0 | S2/1 |

| <b>S3</b> (T4)    | S3/1 | S2/1 |

b) Realizzare la rete sequenziale relativa all'automa minimo con flip flop di tipo SR (5 punti).

### SOLUZIONE:

Anzitutto codifichiamo gli stati nel modo seguente:

$S0 \rightarrow 00$

$S1 \rightarrow 01$

S2 → 10

S3 → 11

Dalla tabella dell'automa minimo, scriviamo ora la tabella degli stati futuri insieme alle funzioni di eccitazione dei FF:

| x Q1 Q0 | Q1' Q0' | z | S1 R1 | SO RO |

|---------|---------|---|-------|-------|

| 0 0 0   | 1 1     | 0 | 1 0   | 1 0   |

| 0 0 1   | 0 1     | 1 | 0 -   | - 0   |

| 0 1 0   | 0 1     | 0 | 0 1   | 1 0   |

| 0 1 1   | 1 1     | 1 | - 0   | - 0   |

| 1 0 0   | 1 0     | 0 | 1 0   | 0 -   |

| 1 0 1   | 0 0     | 1 | 0 -   | 0 1   |

| 1 1 0   | 1 0     | 1 | - 0   | 0 -   |

| 1 1 1   | 1 0     | 1 | - 0   | 0 1   |

Mediante le mappe di Karnaugh (richieste nello svolgimento, ma non riportate per motivi di spazio), ci calcoliamo le espressioni booleane in forma SOP minimale per le entrate dei FF e per l'uscita del circuito:

$$z = Q0 + x Q1$$

$$S1 = \underline{Q0} \underline{Q1}$$

$$R1 = \underline{x} Q1 \underline{Q0}$$

$$S0 = \underline{x}$$

$$R0 = x$$

e da queste bisogna disegnare il circuito (omesso perché banale, ma richiesto all'esame).

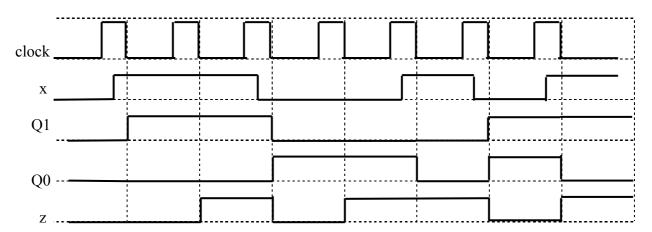

c) Mostrare il diagramma temporale in corrispondenza della stringa di input 1100101 (3 punti).

## Esercizio 3 (8 punti):

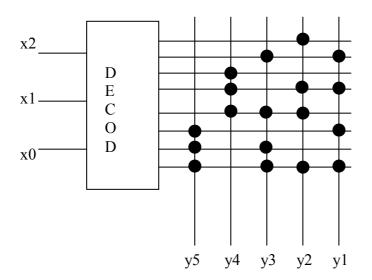

a) Progettare la rete combinatoria che ha sulle linee di ingresso la codifica binaria di un intero x,  $0 \le x \le 7$ , e sulle linee di uscita la codifica binaria di  $y = y_4y_3y_2y_1y_0 = 3x + 2$ , usando una ROM. (3 punti)

#### SOLUZIONE:

La tabella che descrive la funzione richiesta è:

| x2 x1 x0 | <i>y5</i> | <i>y4</i> | у3 | <i>y</i> 2 | <i>y1</i> |  |

|----------|-----------|-----------|----|------------|-----------|--|

| 0 0 0    | 0         | 0         | 0  | 1          | 0         |  |

| 0 0 1    | 0         | 0         | 1  | 0          | 1         |  |

| 0 1 0    | 0         | 1         | 0  | 0          | 0         |  |

| 0 1 1    | 0         | 1         | 0  | 1          | 1         |  |

| 1 0 0    | 0         | 1         | 1  | 1          | 0         |  |

| 1 0 1    | 1         | 0         | 0  | 0          | 1         |  |

| 1 1 0    | 1         | 0         | 1  | 0          | 0         |  |

| 1 1 1    | 1         | 0         | 1  | 1          | 1         |  |

Da essa si ottiene la seguente ROM (con decodificatore):

b) scrivere la forma canonica POS di y2 (1 punto)

M0 M2 M3 M5 =

$$(x^2 + x^1 + x^0)(x^2 + x^1 + x^0)(x^2 + x^1 + x^0)(x^2 + x^1 + x^0)$$

c) scrivere la forma canonica SOP di y3 (1 punto)

$$m2 + m3 + m4 = \underline{x2} \times 1 \times \underline{x0} + \underline{x2} \times 1 \times 0 + x2 \times \underline{x1} \times \underline{x0}$$

d) realizzare y1 con sole porte NAND (3 punti)

Dalle mappe di Karnaugh, si ottiene che  $y1 = x1 x0 + \underline{x1} \underline{x0}$

A questo punto si lavora usando De Morgan e la definizione della negazione con porte NAND

$$x1 x0 + \underline{x1} \underline{x0} = x1 x0 + (\underline{x1 + x0})$$

$$= (\underline{x1 x0}) \text{ NAND } (x1 + x0)$$

$$= (x1 \text{ NAND } x0) \text{ NAND } (\underline{x1} \text{ NAND } \underline{x0})$$

$$= (x1 \text{ NAND } x0) \text{ NAND } ((x1 \text{ NAND } x1) \text{ NAND } (x0 \text{ NAND } x0))$$

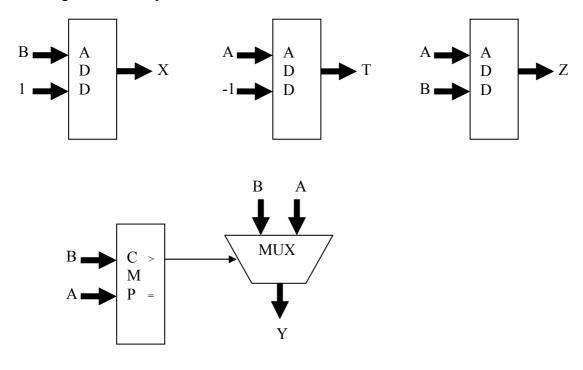

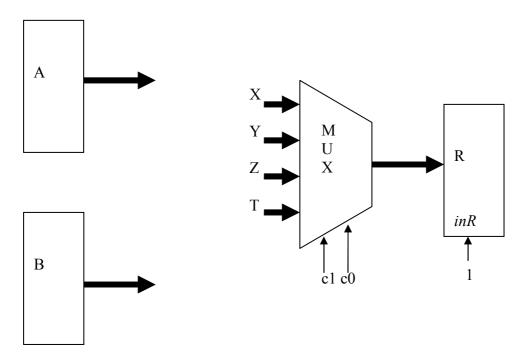

**Esercizio 4 (6 punti)** Dati i registri sorgente A e B contenenti valori nella rappresentazione in complemento a 2, il registro destinazione R e due segnali di controllo, c1c0, progettare il circuito tale che:

- se c1c0=(0,0) trasferisce in R il successore di B

- se c1c0=(0,1) trasferisce in R il massimo tra A e B

- se c1c0=(1,0) trasferisce in R il risultato della somma aritmetica tra A e B

- se c1c0=(1,1) trasferisce in R il predecessore di A

#### SOLUZIONE:

L'interconnessione richiesta è:

dove i quattro ingressi al MUX (con X selezionato se c1 c0 = 00, Y se 01, Z se 10 e T se 11) sono dati dai seguenti circuiti più elementari: